## DDR-I/II Termination Regulator

The NCP5208 is a linear regulator specifically designed for the active termination of DDR–I/II SDRAM. The device can be operated from a single supply voltage as low as 1.7 V. For DDR–I applications, the device is capable of sourcing and sinking current up to 1.5 A with the output voltage regulated to within  $\pm 3\%$  or better. A separate voltage feedback pin ensures superior load regulation against load and line changes.

Protective features include soft-start, source/sink current limits and thermal shutdown. Open-drain VTT OK output ( $\overline{POK}$ ) is added for system monitoring. The shutdown pin can tri-state the regulator output for Suspend To RAM (STR) state. This device is available in a SOIC-8 package.

#### Features

- Supports Both DDR-I and DDR-II SDRAM Requirements

- Single Supply Voltage Operation as Low as 1.7 V

- Integrated Power MOSFETs

- Few External Components Needed

- Source and Sink Current Up to 1.5 A

- Load Regulation Within  $\pm 3\%$

- Both Source and Sink Current Limits

- Open–Drain VTT OK (POK) Pin

- Shutdown Pin

- Thermal Shutdown

- Housed in SOIC–8 Package

- Pb–Free Package is Available

#### **Typical Applications**

- DDR Termination Voltage

- Active Bus Termination (SSTL-2, SSTL-3)

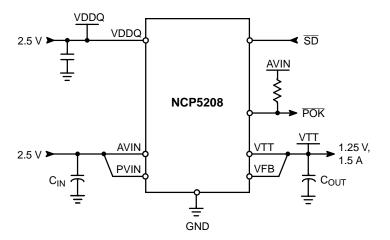

Figure 1. Typical Application Circuit

## **ON Semiconductor®**

http://onsemi.com

#### SOIC-8 D SUFFIX CASE 751

#### MARKING DIAGRAM

A = Assembly Location

- L = Wafer Lot

- Y = Year W = Work W

- W = Work Week

- = Pb–Free Package

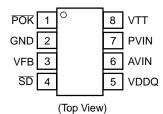

#### **PIN CONNECTIONS**

### **ORDERING INFORMATION**

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| NCP5208DR2  | SOIC-8              | 2500/Tape & Reel      |

| NCP5208DR2G | SOIC-8<br>(Pb-Free) | 2500/Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **PIN FUNCTION DESCRIPTION**

| Pin | Symbol | Description                                                                         |

|-----|--------|-------------------------------------------------------------------------------------|

| 1   | POK    | Open-drain VTT Power OK output                                                      |

| 2   | GND    | Ground                                                                              |

| 3   | VFB    | Remote sensing Feedback pin for regulating VTT                                      |

| 4   | SD     | Active low shutdown pin to tri-state VTT output, this pin is pulled high internally |

| 5   | VDDQ   | Reference input for VTT regulator                                                   |

| 6   | AVIN   | Analog supply input, this powers all the internal control circuitry                 |

| 7   | PVIN   | Power supply input, this provides the rail voltage for the VTT output               |

| 8   | VTT    | Termination Regulator output                                                        |

#### MAXIMUM RATINGS

| Rating                                                                          |     | Symbol            | Value       | Unit |

|---------------------------------------------------------------------------------|-----|-------------------|-------------|------|

| AVIN, PVIN, VDDQ, VFB, VTT to GND                                               |     | -                 | -0.3, 6.0   | V    |

| Input/Output Pins                                                               | SD  | V <sub>IO</sub>   | -0.3, 6.0   | V    |

| Open Drain Output Pins                                                          | POK | V <sub>POK</sub>  | -0.3, 6.0   | V    |

| Thermal Characteristics<br>SOIC–8 Package – Thermal Resistance, Junction–to–Air |     | $R_{\theta JA_T}$ | 151         | °C/W |

| Operating Junction Temperature Range                                            |     | TJ                | -10 to +150 | °C   |

| Operating Ambient Temperature Range                                             |     | T <sub>A</sub>    | 0 to +70    | °C   |

| Storage Temperature Range                                                       |     | T <sub>stg</sub>  | -55 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device series contains ESD protection and exceeds the following tests: Human Body Model (HBM)  $\leq$  2.0 kV per JEDEC standard: JESD22–A114. Machine Model (MM)  $\leq$  200 V per JEDEC standard: JESD22–A115.

2. Latchup Current Maximum Rating: ± 150 mA per JEDEC standard: JESD78.

| ELECTRICAL CHARACTERISTICS (AVIN = 2.5 V, PVIN = 2.5 V, VDDQ = 2.5 V, C <sub>OUT</sub> = 220 μF, for typical values T <sub>A</sub> = 25°C, for |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| min/max values $T_A = 0$ to 70°C, unless otherwise noted.)                                                                                     |  |

| Characteristic                     | Conditions                                                           | Symbol   | Min      | Тур                   | Max      | Unit |  |

|------------------------------------|----------------------------------------------------------------------|----------|----------|-----------------------|----------|------|--|

| Analog Supply Input                | _                                                                    | AVIN     | 1.7      | -                     | 5.5      | V    |  |

| Power Supply Input                 | _                                                                    | PVIN     | 1.7      | -                     | AVIN     | V    |  |

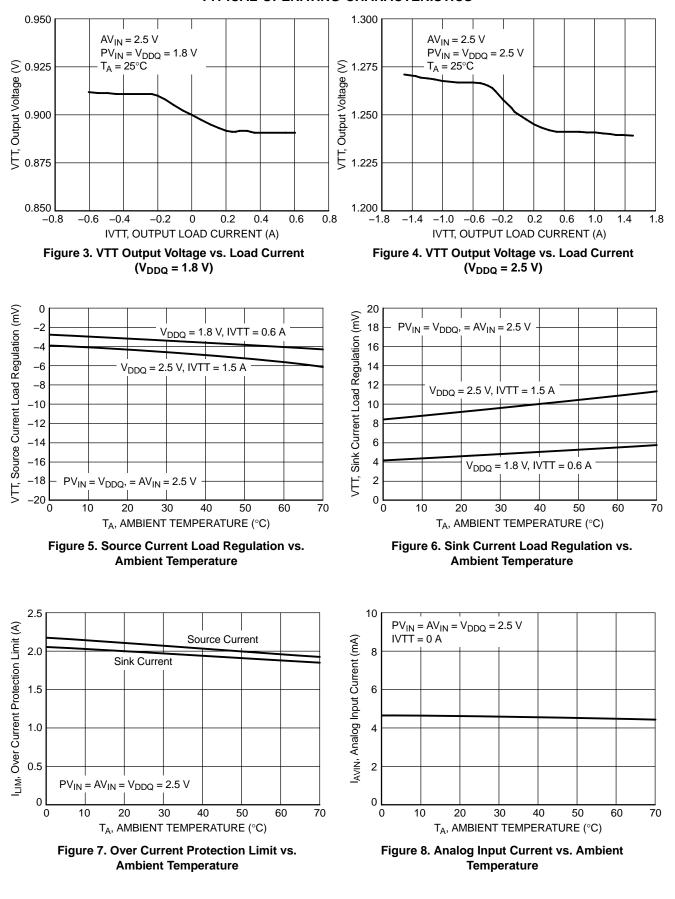

| Termination Voltage Output         | AVIN = 2.5 V, VDDQ = PVIN = 1.8 V<br>IVTT = -0.6 A to +0.6 A         | VTT      | 0.870    | 0.900                 | 0.930    | V    |  |

|                                    | AVIN = PVIN = VDDQ = 2.5 V<br>IVTT = -1.5 A to 1.5 A                 |          | 1.215    | 1.250                 | 1.285    | V    |  |

| Load Regulation                    | VDDQ = 1.8 V, IVTT = 0 to +0.6 A<br>VDDQ = 1.8 V, IVTT = 0 to -0.6 A | Δνττ     | _<br>_18 | -                     | 15<br>-  | mV   |  |

|                                    | VDDQ = 2.5 V, IVTT = 0 to +1.5 A<br>VDDQ = 2.5 V, IVTT = 0 to -1.5 A |          | _<br>_20 | -                     | 20<br>-  | mV   |  |

| Analog Current Consumption         | No Load                                                              | IAVIN    | -        | -                     | 10       | mA   |  |

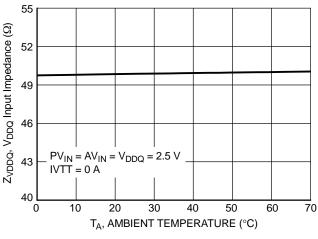

| VDDQ Input Impedance               | _                                                                    | ZVDDQ    | -        | 50                    | -        | kΩ   |  |

| VFB Feedback Pin Input Current     | (Note 3)                                                             | IVFB     | -        | -                     | 20       | nA   |  |

| SHUTDOWN CONTROL                   |                                                                      |          |          |                       |          |      |  |

| Shutdown Pin Enable Threshold      | _                                                                    | VSD      | 1.14     | 1.24                  | 1.34     | V    |  |

| Shutdown Pin Hysteresis            | _                                                                    | VSDhys   | 0.40     | 0.55                  | 0.68     | V    |  |

| Shutdown Pin Input Current         | VDDQ = 2.5 V, VSD = 0 V                                              | ISD      | -15      | -                     | -        | μΑ   |  |

|                                    | VDDQ = 2.5 V, VSD = 2.5 V<br>VDDQ = 2.5 V, VSD = 5.5 V               |          |          | -                     | 10<br>12 |      |  |

| Shutdown Analog Supply Current     | VDDQ = 2.5 V, VSD = 0 V                                              | Ishut    | -        | -                     | 15       | μΑ   |  |

| VTT POWER OK INDICATOR             |                                                                      |          |          |                       |          |      |  |

| VTT Power OK Window Low Threshold  | (Note 4)                                                             | POKLth   | -        | VDDQ ×<br>(1/2–0.02)  | -        | V    |  |

| VTT Power OK Window High Threshold | (Note 4)                                                             | POKHth   | -        | VDDQ ×<br>(1/2+ 0.02) | -        | V    |  |

| POK Pull-LOW Resistance            | IPOK = 5.0 mA                                                        | RPOKL    | 7.0      | -                     | 20       | Ω    |  |

| POK Leakage Current                | VDDQ = 2.5 V, VPOK = 6.0 V                                           | IPOKleak | -        | _                     | 0.1      | μΑ   |  |

| OVER CURRENT PROTECTION            |                                                                      |          |          |                       |          |      |  |

| Source Current Limit               | _                                                                    | ILIMsrc  | 1.65     | 2.1                   | 2.9      | А    |  |

| Sink Current Limit                 | -                                                                    | ILIMsnk  | -2.9     | -2.0                  | -1.65    | А    |  |

| OVER TEMPERATURE PROTECTION        | · ·                                                                  |          | •        | •                     |          |      |  |

| Thermal Shutdown Temperature       | (Note 3)                                                             | TSD      | 120      | 135                   | 150      | °C   |  |

| Thermal Shutdown Hysteresis        | (Note 3)                                                             | TSDhys   | _        | 30                    | -        | °C   |  |

Values are not tested in production, guaranteed by design only.

Production test performed for AVIN = PVIN = VDDQ = 2.5 V only, 1.8 V performance guaranteed by design.

#### **TYPICAL OPERATING CHARACTERISTICS**

#### **TYPICAL OPERATING CHARACTERISTICS**

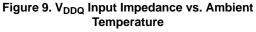

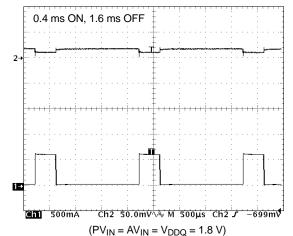

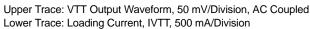

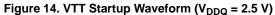

**TYPICAL OPERATING WAVEFORMS**

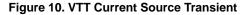

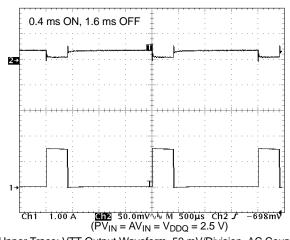

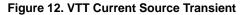

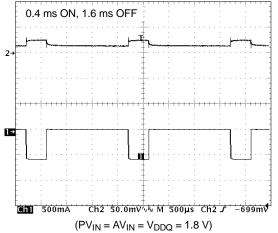

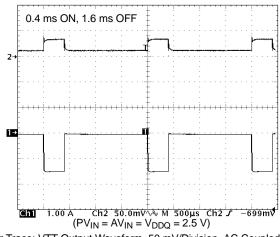

Upper Trace: VTT Output Waveform, 50 mV/Division, AC Coupled Lower Trace: Loading Current, IVTT, 1 A/Division

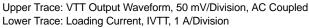

Upper Trace: VTT Output Waveform, 50 mV/Division, AC Coupled Lower Trace: Loading Current, IVTT, 500 mA/Division

Figure 11. VTT Current Sink Transient

## TYPICAL OPERATING WAVEFORMS

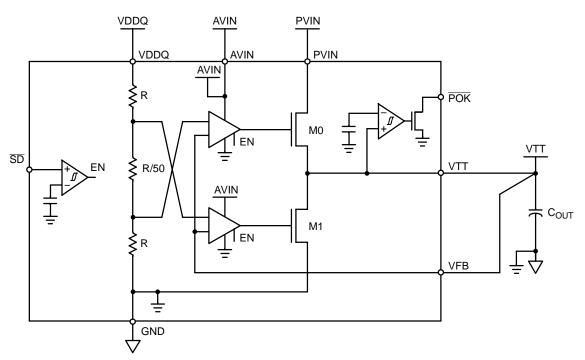

### DETAILED OPERATING DESCRIPTIONS

#### General

The NCP5208 is a linear regulator with both sink and source current capabilities used for active termination of fast switching logic, DDR–I/II SDRAM terminations and active buses termination of SSTL–2/3 logic. This device can be operated from a single supply voltage as low as 1.7 V. For DDR–I applications, the device is capable of sourcing and sinking current up to 1.5 A with output voltage regulated to within  $\pm 3\%$ . The separate voltage remote feedback pin ensures superior load and line regulation with fast tracking capability.

Protective features include Soft–Start, Source/Sink Current Limits and internal Thermal Shutdown. Additionally, an open–drain VTT OK output signal ( $\overline{POK}$ ) is provided for system monitoring. The shutdown pin ( $\overline{SD}$ ) can be used to tri–state the regulator output for Suspend To RAM (STR) state. This device is available in a low profile, space saving SOIC–8 package.

#### **Supply Voltage Inputs**

For added flexibility, separate input pins are provided for each required supply input. AVIN is the device operating voltage, VDDQ is used to generate the internal reference for VTT output voltage control and PVIN is the power rail for the linear regulator. The device will regulate the output voltage, VTT, with respect to the internal voltage reference generated from VDDQ input and track the VDDQ changes closely. The separate PVIN pin allows the designer to isolate the high current PVIN line changes from coupling into the noise sensitive AVIN and VDDQ inputs. Since the AVIN supplies the control to the output power MOSFETs, PVIN should always be lower than or equal to AVIN.

#### **Generation of Internal Reference Voltage**

The prime function of a termination regulator is to provide a termination voltage, VTT at its output, which can track the mid-point of the logic voltage level closely, i.e.  $\frac{1}{2}$ (VDDQ). The VTT voltage is used to terminate the bus resistors. The NCP5208 generates a precise reference voltage internally with a built in dead-band to avoid upper and lower MOSFET shoot through.

#### **Remote Voltage Feedback Sensing**

The NCP5208 has a separate feedback pin to monitor the output voltage at the remote point. With this capability, the output voltage can be controlled precisely at the output capacitor so that any noise and fluctuations along the power path can be eliminated.

#### **Termination Voltage Output Regulation**

The NCP5208 includes a simple linear series regulator with a pair of control error amplifiers, which takes care of the current source and sink operations separately. The error amplifiers control a pair of MOSFETs to maintain the output voltage equal to the internal reference voltage for both current sink and source conditions. In order to avoid the MOSFETs turning on at the same time, a dead–band is implemented internally for safe operation.

#### **Regulator Shutdown Function**

The operation of the NCP5208 can be suspended by pulling the Shutdown  $(\overline{SD})$  pin to ground. When the device is stopped, the regulator output will be tri–stated for Suspend To RAM (STR) state in PC applications. The shutdown pin is internally pulled high by a small current source, if this feature is not used, this pin can be left open.

#### VTT Power OK for System Monitoring

NCP5208 provides an additional VTT power OK signal for system monitoring. The VTT Power OK ( $\overrightarrow{POK}$ ) pin goes low when the VTT voltage is in regulation and has settled within the allowed window. For memory termination applications, the system can check this pin to ensure the termination voltage quality before accessing the memory. The  $\overrightarrow{POK}$  output is connected to a open-drain switching FET and the designer is free to pull this pin to any logic voltage level externally. When the VTT output is in regulation, the internal FET is turned on and pulls the power OK pin to ground.

### **Over-current Protection for Sink and Source Operation**

In order to provide protection for the internal power MOSFETs, bi-directional current limit protection circuits are implemented. Current limit levels are internally set at 2.1 A typical for current source and 2.0 A typical for current sink at 2.5 V operation.

#### Thermal Shutdown with Hysteresis

To guarantee safe operation, NCP5208 provides on-chip thermal shutdown protection. When the chip junction temperature exceeds  $135^{\circ}$ C typical, the part will shutdown. When the junction temperature falls back to  $105^{\circ}$ C typical, the device resumes normal operation.

#### APPLICATIONS INFORMATION

#### **Typical Application Circuit**

The NCP5208 is a highly integrated termination regulator. For most applications, an input and output capacitor and a pullup resistor for the power OK output, are the only external components needed. For typical application circuit, refer to Figure 1.

#### AVIN and VDDQ Supply

AVIN provides power for the device to operate. This voltage must be kept clean and free from transients. A small capacitor,  $1.0 \ \mu\text{F}$  is recommended at this input to provide the required supply filtering and ripple rejection. VDDQ is primarily used to generate the internal voltage reference, so any noise or transient at this pin will be directly reflected at the VTT output. In order to avoid undesired interference injected into this pin, appropriate de-coupling and careful design of PCB layout is required.

#### Input Capacitor Selection

The NCP5208 does not require an input capacitor for stability, however it is still recommended for better overall performance during large load transients that can cause sudden drop of the power rail voltage. The input capacitor must be located as close as possible to the PVIN pin to avoid a transient voltage dip affecting the quality of AVIN and VDDQ. For typical DDR–I applications, a low ESR electrolytic capacitor of 100  $\mu$ F or larger is recommended. By adding a small ceramic capacitor of 0.1  $\mu$ F in parallel, the best high frequency transient filtering will result. If the device is located near the main supply bulk capacitors, the input capacitance can be reduced accordingly.

#### **Output Capacitor Selection**

The NCP5208 is internally compensated and stable for any output capacitor with capacitance greater than 220  $\mu$ F and with ESR ranging from 2 m $\Omega$  to 400 m $\Omega$ . The choice for this output capacitor is determined solely by the application and the requirements for load transient characteristic of VTT output. As a general recommendation, the capacitance should be larger than 220  $\mu$ F with low ESR for SSTL and DDR memory applications.

#### Thermal Dissipation

The NCP5208 is a linear regulator, any current flow from/to VTT will result in internal power dissipation and generating heat. In order to prevent un–wanted shutdown of the device during operation, care should be taken to de–rate the power capability according to the maximum expected ambient temperature and power dissipation. The maximum allowable internal temperature rise,  $T_{R-MAX}$  can be calculated from the equation in below:

### $T_{R-MAX} = T_{J-MAX} - T_{A-MAX}$

Where  $T_{J-MAX}$  is the maximum allowable junction temperature and  $T_{A-MAX}$  is the maximum expected ambient temperature.

The maximum allowable power dissipation for a specific condition is given by:

$$\mathsf{P}_{\mathsf{D}-\mathsf{MAX}} = \frac{\mathsf{T}_{\mathsf{R}-\mathsf{MAX}}}{\mathsf{R}_{\theta}\mathsf{J}\mathsf{A}_{-}\mathsf{T}}$$

Where  $P_{D-MAX}$  is the maximum allowable power dissipation and  $R_{\theta JA_T}$  is Junction-to-Air thermal resistance for specific package.

The thermal handling capability depends on several variables. Increasing the thickness and area of the copper and adding vias and airflow can improve the thermal performance.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B            | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DESCRIPTION: SOIC-8 NB |                                                                                                                                                                                    |  |  |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights or the |                        |                                                                                                                                                                                    |  |  |  |  |

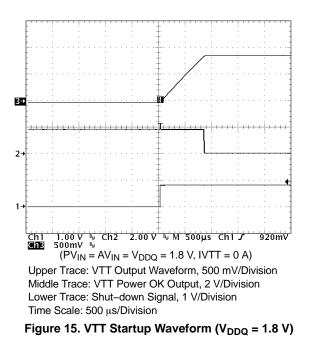

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER EMITTER 5. BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: CATHODE 1 PIN 1. 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: PIN 1. GROUND BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC COMMON CATHODE/VCC 3 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 COMMON ANODE/GND 8. STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. 4. DRAIN, #2 GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 DRAIN 1 7. 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. SOURCE SOURCE 6. SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: ANODE ANODE PIN 1. 2. ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 3. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. 4. GATE 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B            | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DESCRIPTION: SOIC-8 NB |                                                                                                                                                                                     | PAGE 2 OF 2 |  |  |

| ON Semiconductor and () are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                        |                                                                                                                                                                                     |             |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

7.

8

rights of others

COLLECTOR, #1

COLLECTOR, #1

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor houteds for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative