# **MSC8156 Reference Manual**

Six Core Digital Signal Processor

MSC8156RM Rev 2, June 2011

### How to Reach Us:

#### Home Page:

www.freescale.com

## Web Support:

http://www.freescale.com/support

## **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

## Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 010 5879 8000

support.asia@freescale.com

## For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

+1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, and CodeWarrior are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. QUICC Engine is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2009-2011 Freescale Semiconductor, Inc.

MSC8156RM Rev. 2 6/2011

| 1  | Overview                                              |

|----|-------------------------------------------------------|

| 2  | SC3850 Core Overview                                  |

| 3  | External Signals                                      |

| 4  | Chip-Level Arbitration and Switching System (CLASS)   |

| 5  | Reset                                                 |

| 6  | Boot Program                                          |

| 7  | Clocks                                                |

| 8  | General Configuration Registers                       |

| 9  | Memory Map                                            |

| 10 | MSC8154 SC3850 DSP Subsystem                          |

| 11 | Internal Memory Subsystem                             |

| 12 | DDR-SDRAM Controller                                  |

| 13 | Interrupt Handling                                    |

| 14 | Direct Memory Access (DMA) Controller                 |

| 15 | High Speed Serial Interface (HSSI)                    |

| 16 | Serial RapidIO Controller                             |

| 17 | PCI Express Controller                                |

| 18 | QUICC Engine Subsystem                                |

| 19 | TDM Interface                                         |

| 20 | UART                                                  |

| 21 | Timers                                                |

| 22 | GPIO                                                  |

| 23 | Hardware Semaphores                                   |

| 24 | I <sup>2</sup> C                                      |

| 25 | Debugging, Profiling, and Performance Monitoring      |

| 26 | Multi Accelerator Platform Engine, Baseband (MAPLE-B) |

23

24

I<sup>2</sup>C

| <b>VP</b> |                                                     |

|-----------|-----------------------------------------------------|

| 1         | Overview                                            |

| 2         | SC3850 Core Overview                                |

| 3         | External Signals                                    |

| 4         | Chip-Level Arbitration and Switching System (CLASS) |

| 5         | Reset                                               |

| 6         | Boot Program                                        |

| 7         | Clocks                                              |

| 8         | General Configuration Registers                     |

| 9         | Memory Map                                          |

| 10        | MSC8154 SC3850 DSP Subsystem                        |

| 11        | Internal Memory Subsystem                           |

| 12        | DDR-SDRAM Controller                                |

| 13        | Interrupt Handling                                  |

| 14        | Direct Memory Access (DMA) Controller               |

| 15        | High Speed Serial Interface (HSSI)                  |

| 16        | Serial RapidIO Controller                           |

| 17        | PCI Express Controller                              |

| 18        | QUICC Engine Subsystem                              |

| 19        | TDM Interface                                       |

| 20        | UART                                                |

| 21        | Timers                                              |

| 22        | GPIO                                                |

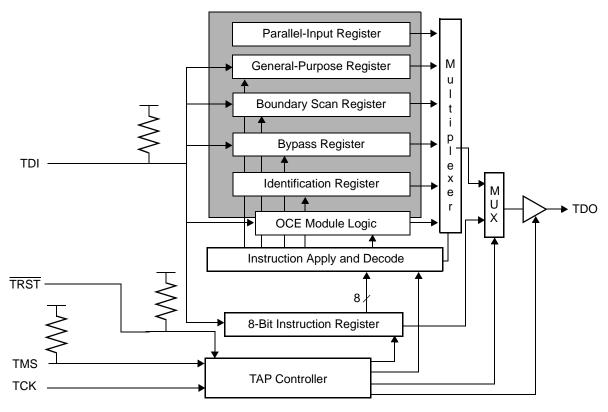

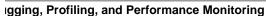

25 **Debugging, Profiling, and Performance Monitoring**

**Hardware Semaphores**

26 Multi Accelerator Platform Engine, Baseband (MAPLE-B)

|          | About This Book                                          |

|----------|----------------------------------------------------------|

|          | Before Using This Manual—Important Note xli              |

|          | Audience and Helpful Hints xli                           |

|          | Notational Conventions and Definitions                   |

|          | Conventions for Registers                                |

|          | Organizationxliv                                         |

|          | Other MSC8156 Documentationxlvi                          |

|          | Further Reading xlvi                                     |

|          | Document Change Historyxlvii                             |

| 1        | Overview                                                 |

| 1.1      | Features                                                 |

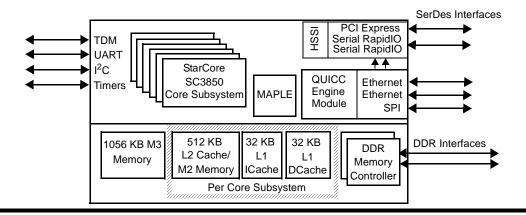

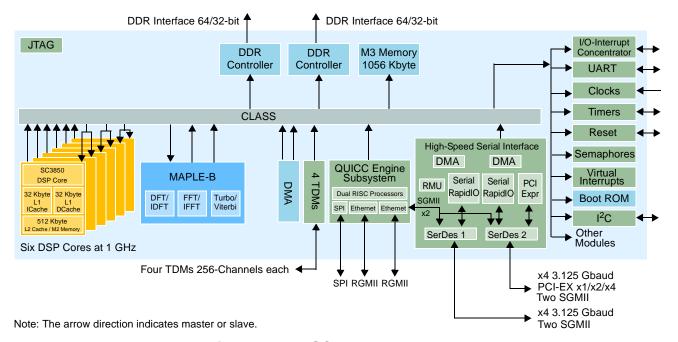

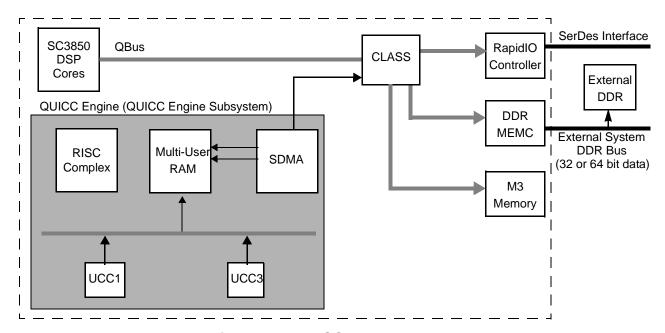

| 1.2      | Block Diagram                                            |

| 1.3      | Architecture                                             |

| 1.4      | StarCore SC3850 DSP Subsystem                            |

| 1.4.1    | Enhancements                                             |

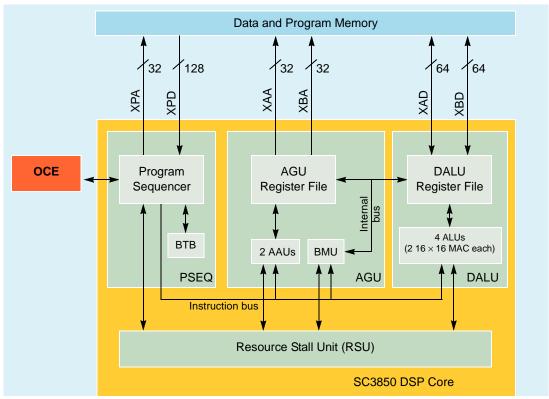

| 1.4.2    | StarCore SC3850 DSP Core                                 |

| 1.4.3    | L1 Instruction Cache                                     |

| 1.4.4    | L1 Data Cache1-17                                        |

| 1.4.5    | L2 Unified Cache/M2 Memory1-18                           |

| 1.4.6    | Memory Management Unit (MMU)                             |

| 1.4.7    | Debug and Profiling Unit (DPU)                           |

| 1.4.8    | Extended Programmable Interrupt Controller               |

| 1.4.9    | Timer                                                    |

| 1.5      | MAPLE-B                                                  |

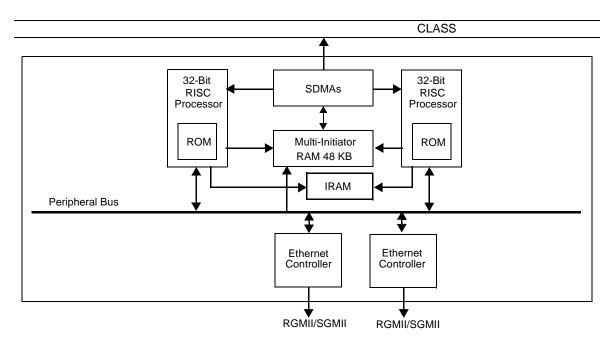

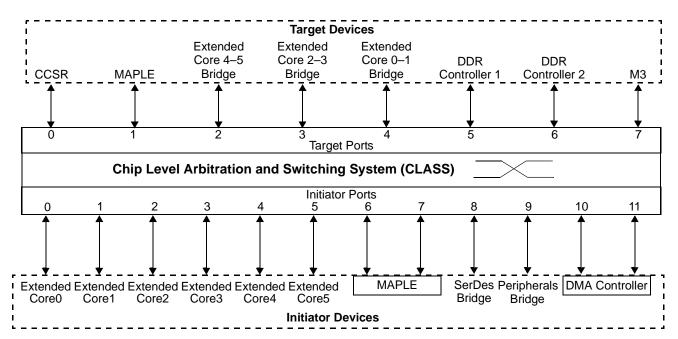

| 1.6      | Chip-Level Arbitration and Switching System (CLASS) 1-20 |

| 1.7      | M3 Memory                                                |

| 1.8      | Clocks                                                   |

| 1.9      | DDR Controllers (DDRC1 and DDRC2)1-21                    |

| 1.10     | DMA Controller                                           |

| 1.11     | High Speed System Interface1-22                          |

| 1.11.1   | Serial RapidIO Subsystem                                 |

| 1.11.1.1 | Serial RapidIO and Host Interactions1-24                 |

| 1.11.1.2 | RapidIO Messaging Unit (RMU) Operation                   |

|          |                                                          |

| 1.11.2 | PCI Express                                                         | 1-26  |

|--------|---------------------------------------------------------------------|-------|

| 1.11.3 | OCN-DMA Controllers                                                 | 1-27  |

| 1.11.4 | OCN Fabric                                                          | 1-27  |

| 1.11.5 | SRIO Port Controller Modules (SRIOn)                                | 1-27  |

| 1.11.6 | SerDes PHY Interfaces                                               | 1-27  |

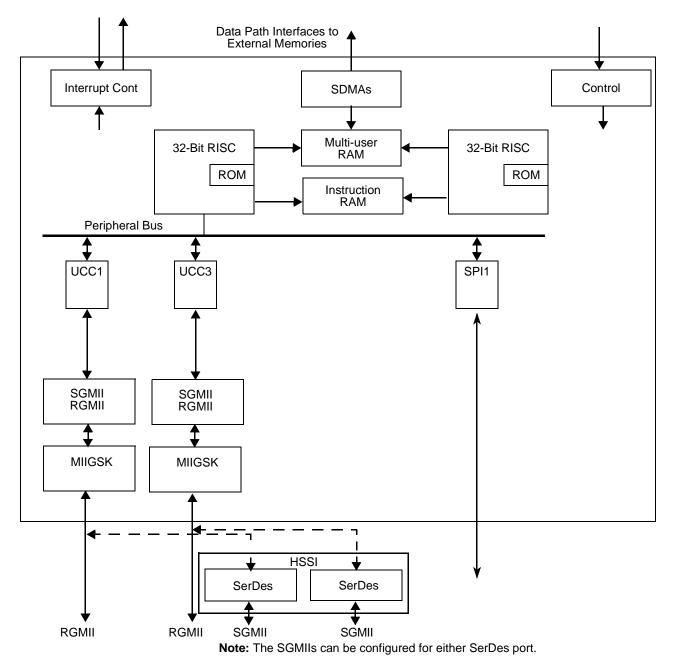

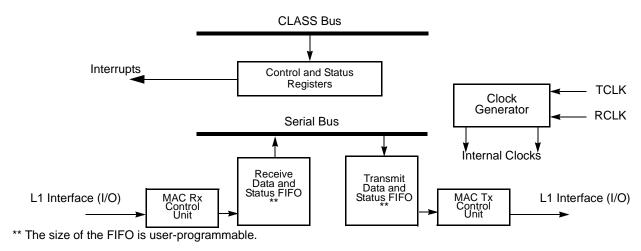

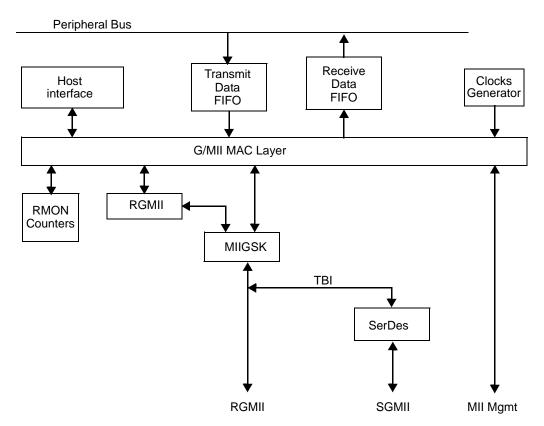

| 1.12   | QUICC Engine Subsystem                                              | 1-28  |

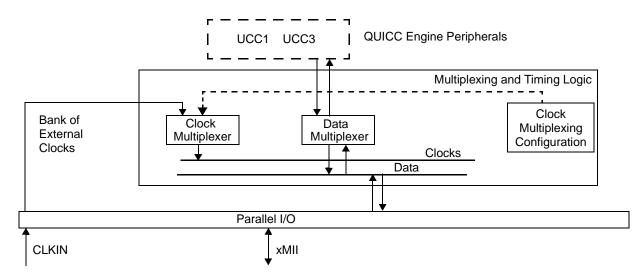

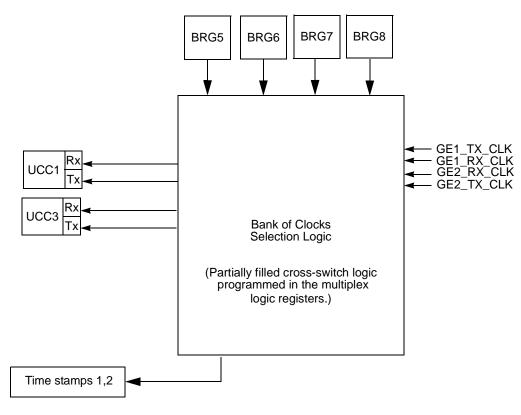

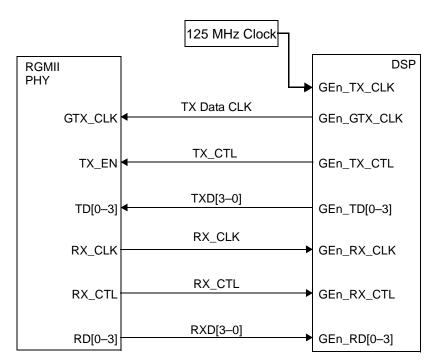

| 1.12.1 | Ethernet Controllers                                                | 1-29  |

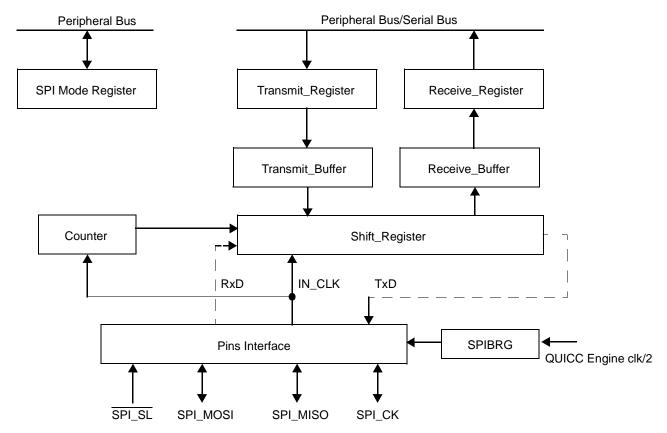

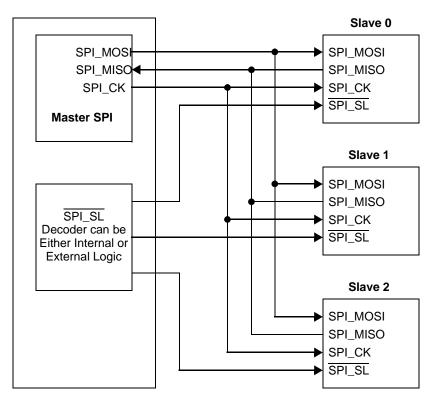

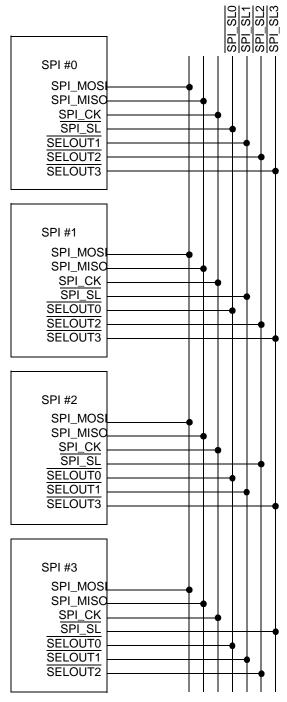

| 1.12.2 | Serial Peripheral Interface (SPI)                                   | 1-30  |

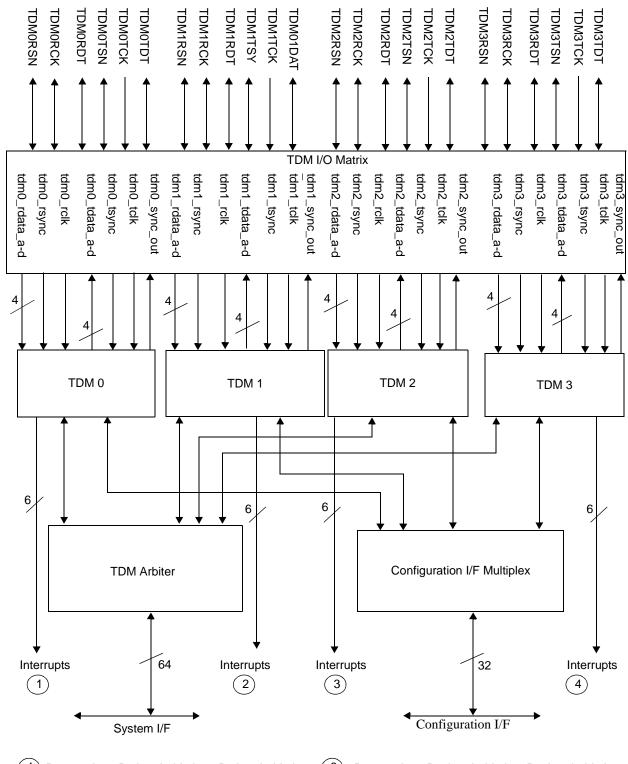

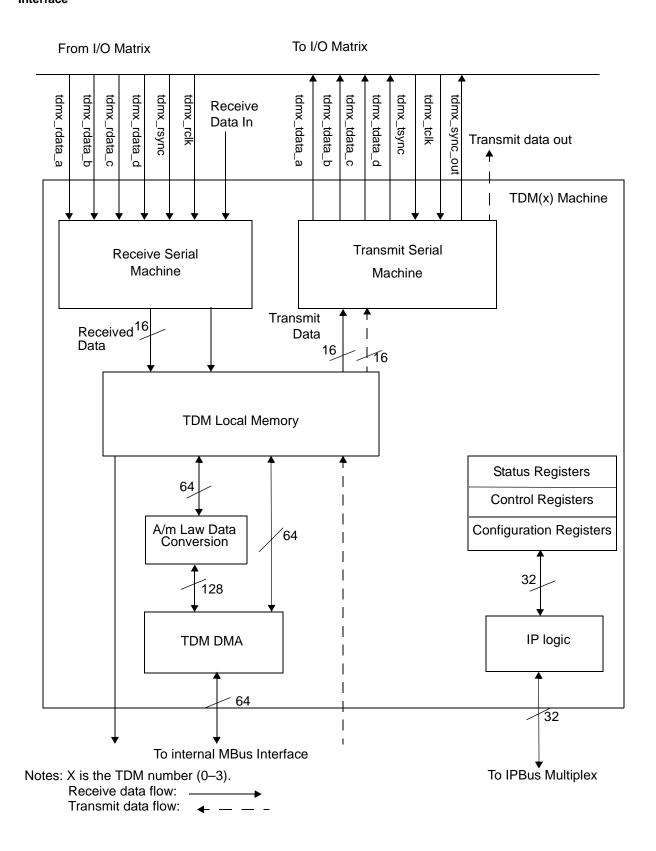

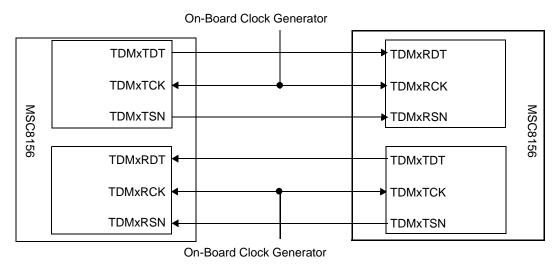

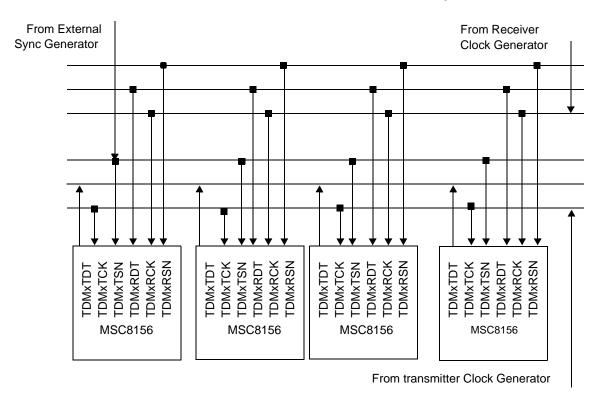

| 1.13   | TDM                                                                 | 1-30  |

| 1.14   | Global Interrupt Controller (GIC)                                   | 1-31  |

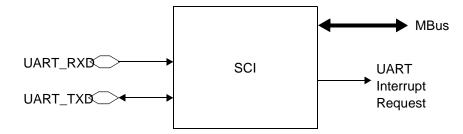

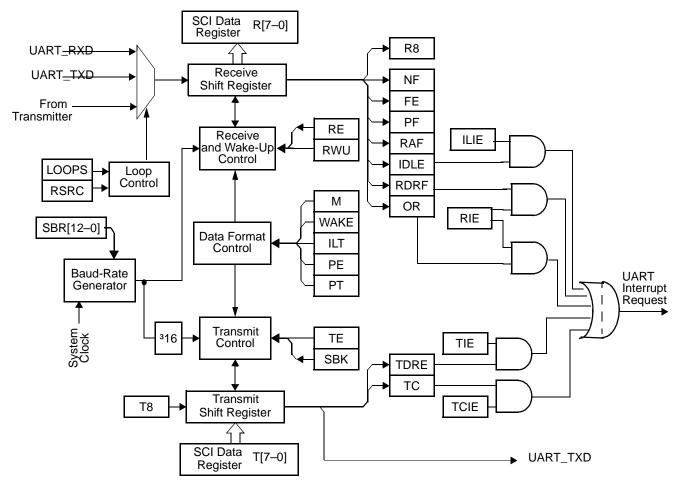

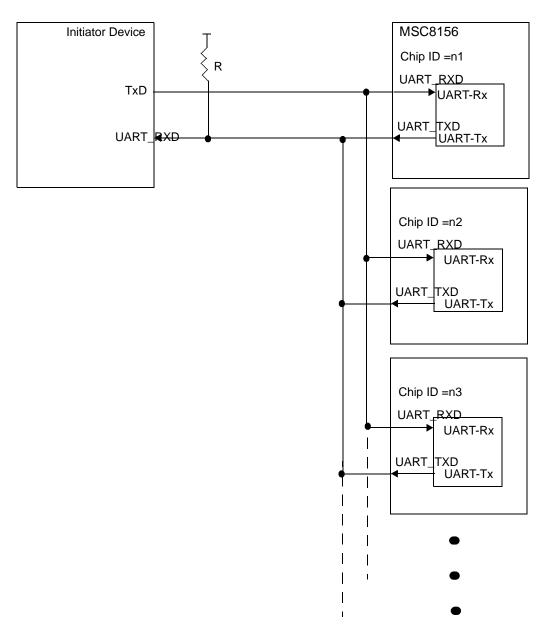

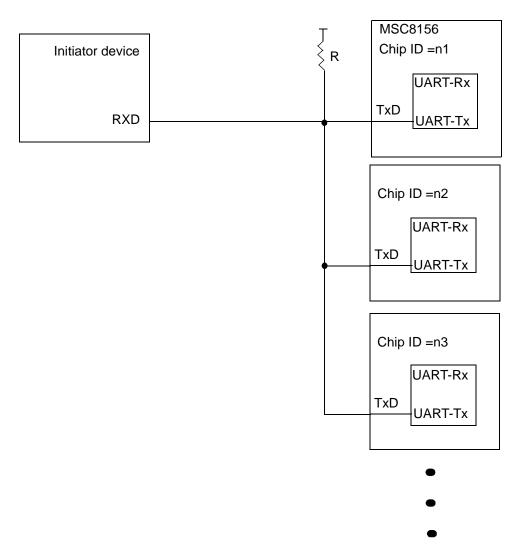

| 1.15   | UART                                                                | 1-31  |

| 1.16   | Timers                                                              | 1-31  |

| 1.17   | Hardware Semaphores                                                 | 1-31  |

| 1.18   | Virtual Interrupts                                                  | 1-32  |

| 1.19   | I <sup>2</sup> C Interface                                          | 1-32  |

| 1.20   | GPIOs                                                               | 1-32  |

| 1.21   | Boot Options                                                        | 1-32  |

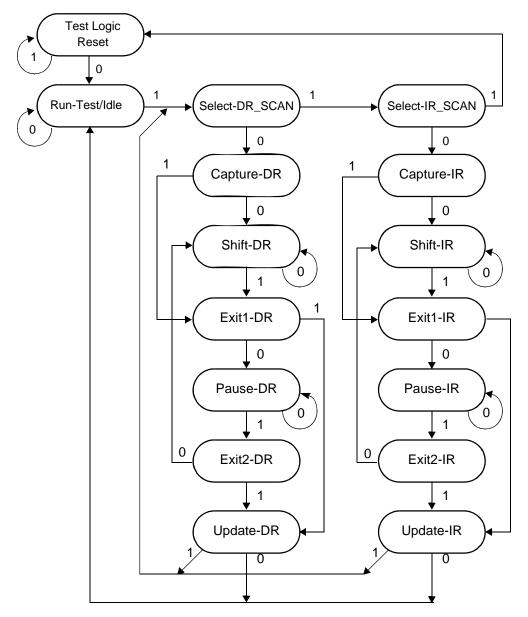

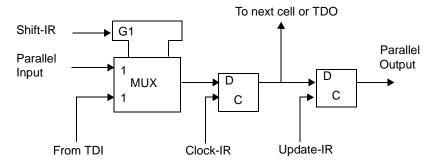

| 1.22   | JTAG                                                                | 1-33  |

| 1.23   | Developer Environment                                               | 1-34  |

| 1.23.1 | Tools                                                               | 1-34  |

| 1.23.2 | Application Software                                                | 1-35  |

| 1.24   | Example Applications                                                | 1-35  |

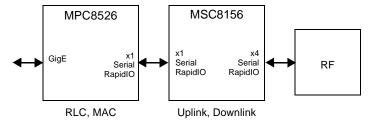

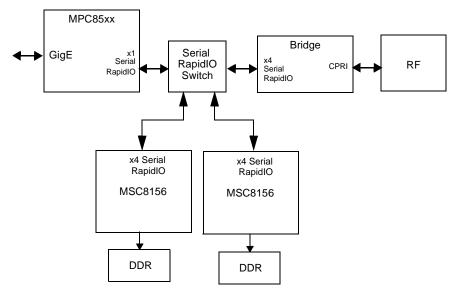

| 1.24.1 | Use Case 1: 3G-LTE Basic System                                     | 1-35  |

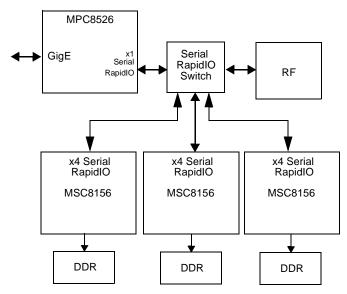

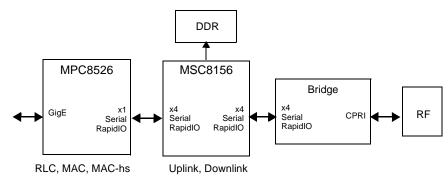

| 1.24.2 | Use Case 2: 3G-LTE System                                           | 1-36  |

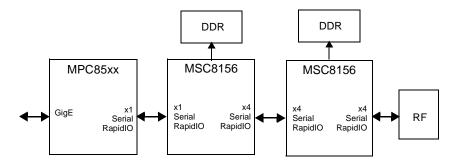

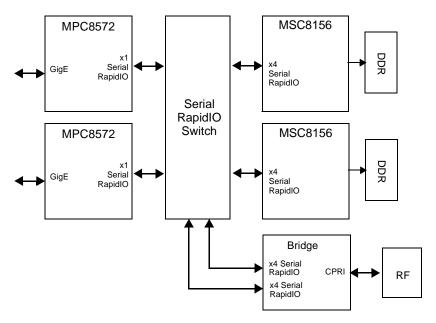

| 1.24.3 | Use Case 3: 3G-LTE System                                           | 1-36  |

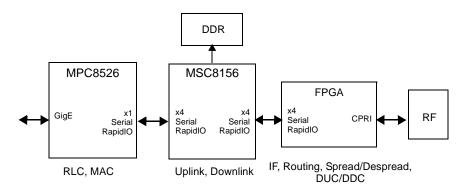

| 1.24.4 | Use Case 4: TD-SCDMA System                                         | 1-37  |

| 1.24.5 | Use Case 5: WiMAX Basic System                                      | 1-37  |

| 1.24.6 | Use Case 6: WiMAX System                                            |       |

| 1.24.7 | Use Case 7: WCDMA Basic System                                      | 1-38  |

| 2      | SC3850 Core Overview                                                |       |

| 2.1    | Core Architecture Features                                          | . 2-2 |

| 2.2    | StarCore SC3850 Core Architecture                                   | . 2-4 |

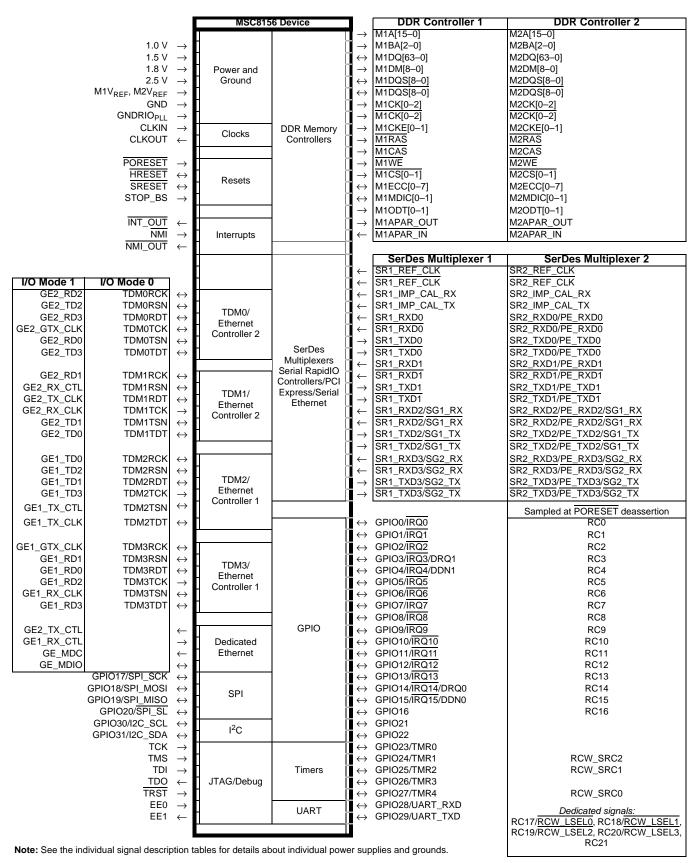

| 3      | External Signals                                                    |       |

| 3.1    | Power Signals                                                       | . 3-4 |

| 3.2    | Clock Signals                                                       |       |

| 3.3    | Reset and Configuration Signals                                     |       |

| 3.4    | Memory Controller 1 and 2                                           |       |

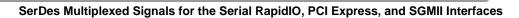

| 3.5    | SerDes Multiplexed Signals for the Serial RapidIO, PCI Express, and |       |

|        |                                                                     | 3-11  |

vi Freescale Semiconductor

| 3.6       | TDM and Ethernet Signals                                    | 3-16 |

|-----------|-------------------------------------------------------------|------|

| 3.7       | Serial Peripheral Interface (SPI) Signal Summary            | 3-20 |

| 3.8       | GPIO/Maskable Interrupt Signal Summary                      | 3-20 |

| 3.9       | Timer Signals                                               | 3-25 |

| 3.10      | UART Signals                                                | 3-26 |

| 3.11      | I <sup>2</sup> C Signals                                    | 3-26 |

| 3.12      | External DMA Signals                                        | 3-27 |

| 3.13      | Other Interrupt Signals                                     | 3-28 |

| 3.14      | OCE Event and JTAG Test Access Port Signals                 | 3-29 |

| 4         | Chip-Level Arbitration and Switching System (CLASS)         |      |

| 4.1       | CLASS Features                                              | 12   |

| 4.1       | Functional Description                                      |      |

| 4.2.1     | Expander Module and Transaction Flow                        |      |

| 4.2.2     | Multiplexer and Arbiter Module                              |      |

| 4.2.2.1   | CLASS Arbiter                                               |      |

| 4.2.2.1.1 | Weighted Arbitration                                        |      |

| 4.2.2.1.2 | Late Arbitration                                            |      |

| 4.2.2.1.3 | Priority Masking                                            |      |

| 4.2.2.1.4 | Auto Priority Upgrade                                       |      |

| 4.2.2.2   | CLASS Multiplexer                                           |      |

| 4.2.3     | Normalizer Module                                           |      |

| 4.2.4     | CLASS Control Interface (CCI)                               |      |

| 4.3       | MSC8156 Initiator CLASS Access Priorities                   |      |

| 4.4       | CLASS Error Interrupts                                      |      |

| 4.5       | CLASS Debug Profiling Unit                                  |      |

| 4.5.1     | Profiling                                                   |      |

| 4.5.2     | Watch Point Unit                                            |      |

| 4.5.3     | Event Selection                                             |      |

| 4.5.4     | Debug and Profiling Events                                  | 4-14 |

| 4.6       | CLASS Reset                                                 | 4-14 |

| 4.6.1     | Soft Reset                                                  | 4-14 |

| 4.6.2     | Hard Reset                                                  | 4-14 |

| 4.7       | Limitations                                                 | 4-14 |

| 4.8       | Programming Model                                           | 4-15 |

| 4.8.1     | CLASS Priority Mapping Registers (C0PMRx)                   | 4-16 |

| 4.8.2     | CLASS Priority Auto Upgrade Value Registers (C0PAVRx)       | 4-18 |

| 4.8.3     | CLASS Priority Auto Upgrade Control Registers (C0PACRx)     | 4-19 |

| 4.8.4     | CLASS Error Address Registers (C0EARx)                      |      |

| 4.8.5     | CLASS Error Extended Address Registers (C0EEARx)            | 4-21 |

| 4.8.6     | CLASS Initiator Profiling Configuration Registers (C0IPCRx) | 4-23 |

MSC8156 Reference Manual, Rev. 2

Freescale Semiconductor vii

| 4.8.7     | CLASS Initiator Watch Point Control Registers (C0IWPCRx)              | 4-25         |

|-----------|-----------------------------------------------------------------------|--------------|

| 4.8.8     | CLASS Arbitration Weight Registers (C0AWRx)                           | 4-2 <i>e</i> |

| 4.8.9     | CLASSO Start Address Decoder x (COSADx)                               | 4-27         |

| 4.8.10    | CLASS End Address Decoder x (C0EADx)                                  | 4-28         |

| 4.8.11    | CLASS Attributes Decoder x (C0ATDx)                                   | 4-29         |

| 4.8.12    | CLASS IRQ Status Register (C0ISR)                                     | 4-30         |

| 4.8.13    | CLASS IRQ Enable Register (C0IER)                                     | 4-31         |

| 4.8.14    | CLASS Target Profiling Configuration Register (COTPCR)                | 4-32         |

| 4.8.15    | CLASS Profiling Control Register (C0PCR)                              | 4-33         |

| 4.8.16    | CLASS Watch Point Control Registers (C0WPCR)                          | 4-34         |

| 4.8.17    | CLASS Watch Point Access Configuration Register (COWPACR)             | 4-36         |

| 4.8.18    | CLASS Watch Point Extended Access Configuration Register              |              |

|           | (COWPEACR)                                                            |              |

| 4.8.19    | CLASS Watch Point Address Mask Registers (C0WPAMR)                    |              |

| 4.8.20    | CLASS Profiling Time-Out Registers (C0PTOR)                           |              |

| 4.8.21    | CLASS Target Watch Point Control Registers (C0TWPCR)                  |              |

| 4.8.22    | CLASS Profiling IRQ Status Register (C0PISR)                          |              |

| 4.8.23    | CLASS Profiling IRQ Enable Register (C0PIER)                          |              |

| 4.8.24    | CLASS Profiling Reference Counter Register (C0PRCR)                   |              |

| 4.8.25    | CLASS Profiling General Counter Registers (C0PGCRx)                   |              |

| 4.8.26    | CLASS Arbitration Control Register (C0ACR)                            | 4-44         |

| 5         | Reset                                                                 |              |

| 5.1       | Reset Operations                                                      | 5 1          |

| 5.1.1     | Reset Sources                                                         |              |

| 5.1.2     | Reset Actions.                                                        |              |

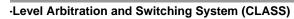

| 5.1.3     | Power-On Reset Flow                                                   |              |

| 5.1.4     | Detailed Power-On Reset Flow                                          |              |

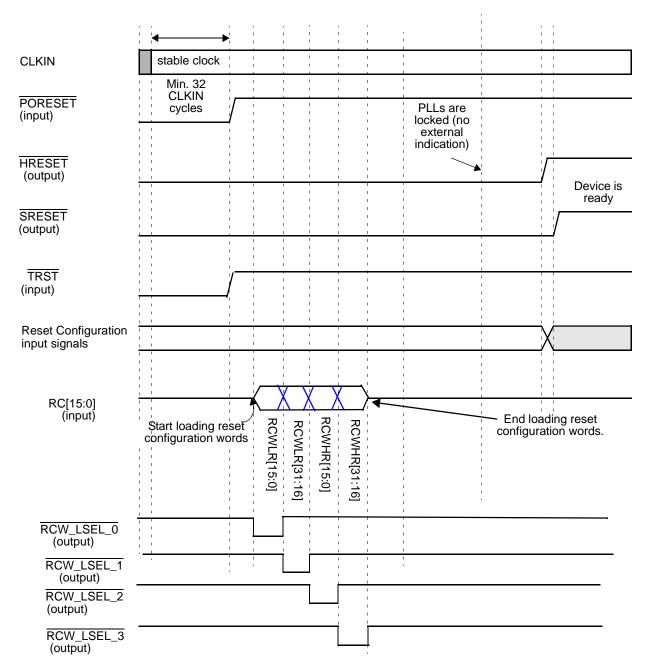

| 5.1.4     | HRESET Flow.                                                          |              |

| 5.1.6     | SRESET Flow                                                           |              |

| 5.2       | Reset Configuration                                                   |              |

| 5.2.1     | Reset Configuration Signals                                           |              |

| 5.2.2     | Reset Configuration Words Source                                      |              |

| 5.2.3     | Reset Configuration Input Signal Selection and Reset Sequence Duratio |              |

| 5.2.4     | Reset Configuration Words                                             |              |

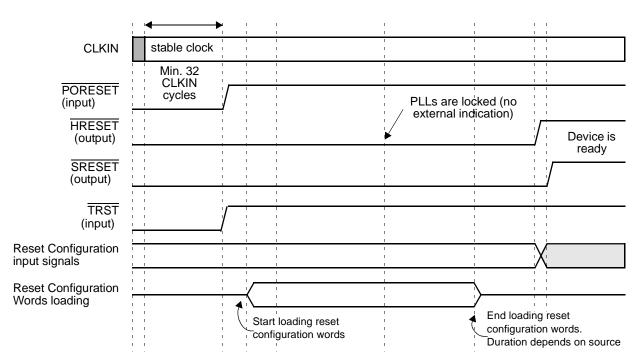

| 5.2.5     | Loading The Reset Configuration Words                                 |              |

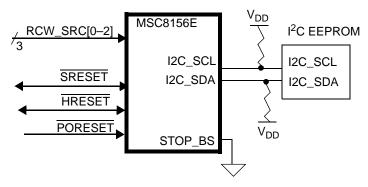

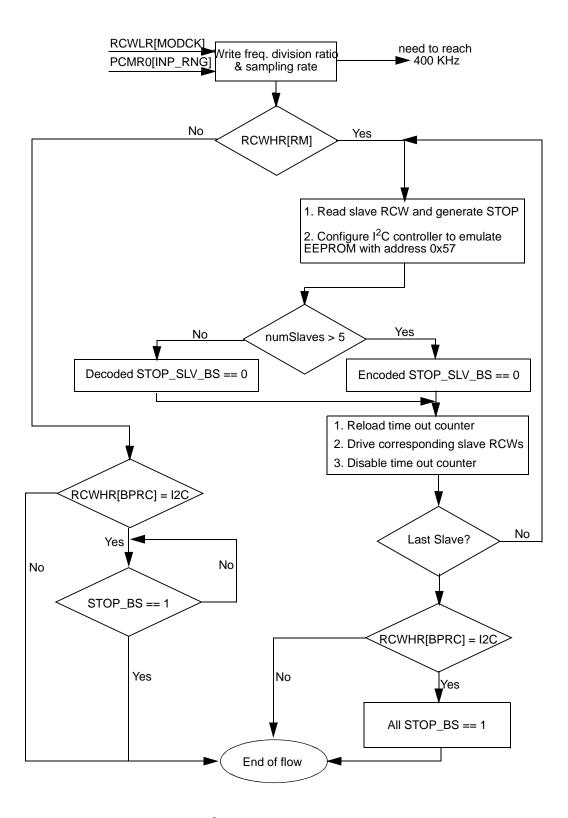

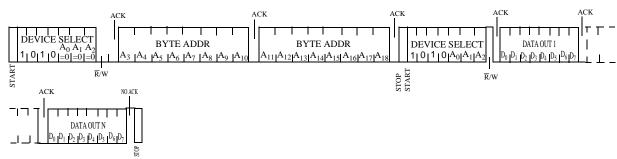

| 5.2.5.1   | Loading From an I2C EEPROM (RCW_SRC[0-2] = 001 or 010)                |              |

| 5.2.5.1.1 | Using The Boot Sequencer For Reset Configuration                      |              |

| 5.2.5.1.1 | EEPROM Slave Address                                                  |              |

| 5.2.5.1.2 | EEPROM Stave Address EEPROM Data Format In Reset Configuration Mode   |              |

| 5.2.5.1.3 |                                                                       |              |

| J.4.J.1.4 | Single Device Loading From I2C EEPROM                                 | J-11         |

viii MSC8156 Reference Manual, Rev. 2

Freescale Semiconductor

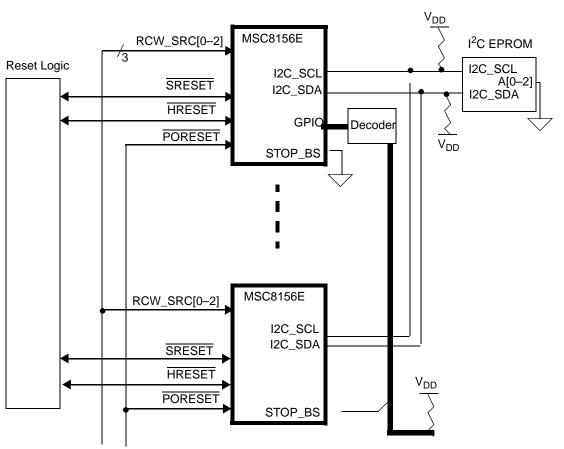

| 5.2.5.1.5 | Loading Multiple Devices From a Single I <sup>2</sup> C EEPROM   | 5-11  |

|-----------|------------------------------------------------------------------|-------|

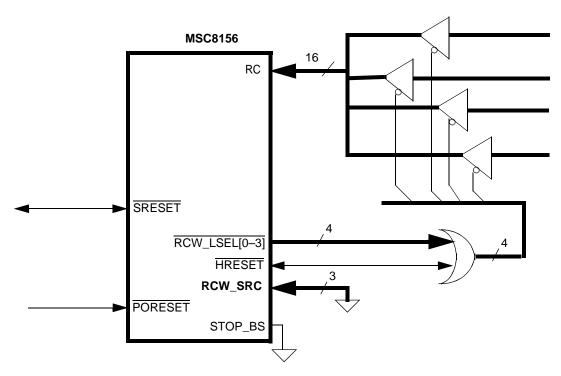

| 5.2.5.2   | Loading Multiplexed RCW from External Pins (RCW_SRC[0-2] = 000). | 5-13  |

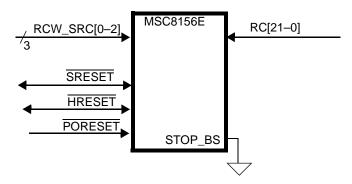

| 5.2.5.3   | Loading Reduced RCW From External Pins (RCW_SRC[0-2] = 011)      | 5-14  |

| 5.2.5.3.1 | Reduced External Reset Configuration Word Low Field Values       | 5-14  |

| 5.2.5.3.2 | Reduced External Reset Configuration Word High Field Values      | 5-15  |

| 5.2.5.4   | Default Reset Configuration Words (RCW_SRC[0-2] = 100 or 101)    | 5-15  |

| 5.2.5.4.1 | Hard Coded Reset Configuration Word Low Field Values             | 5-15  |

| 5.2.5.4.2 | Hard Coded Reset Configuration Word High Field Values            | 5-16  |

| 5.3       | Reset Programming Model                                          |       |

| 5.3.1     | Reset Configuration Word Low Register (RCWLR)                    |       |

| 5.3.2     | Reset Configuration Word High Register (RCWHR)                   | 5-19  |

| 5.3.3     | Reset Status Register (RSR)                                      |       |

| 5.3.4     | Reset Protection Register (RPR)                                  |       |

| 5.3.5     | Reset Control Register (RCR)                                     | 5-25  |

| 5.3.6     | Reset Control Enable Register (RCER)                             | 5-26  |

| 6         | Boot Program                                                     |       |

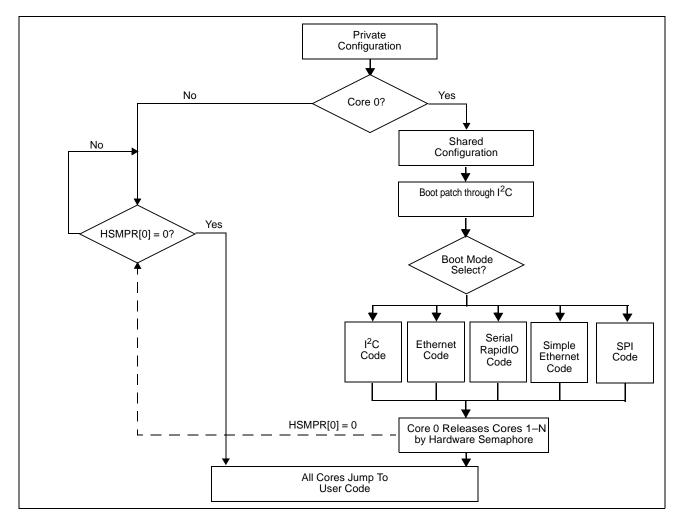

| 6.1       | Functional Description                                           | . 6-2 |

| 6.1.1     | Private Configuration                                            |       |

| 6.1.2     | Shared Configuration                                             |       |

| 6.1.3     | Patch Mode                                                       |       |

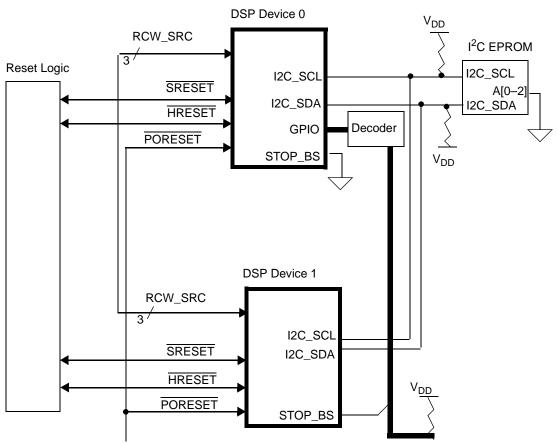

| 6.1.4     | Multi Device Support for the I <sup>2</sup> C Bus                |       |

| 6.1.5     | Example Configuration                                            |       |

| 6.2       | Boot Modes                                                       | . 6-9 |

| 6.2.1     | I <sup>2</sup> C EEPROM                                          |       |

| 6.2.2     | Ethernet                                                         | 6-13  |

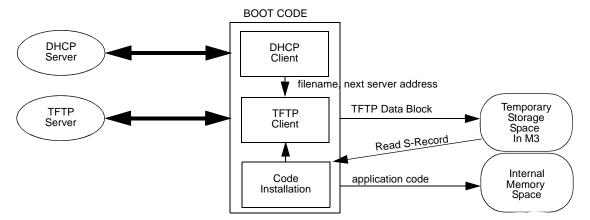

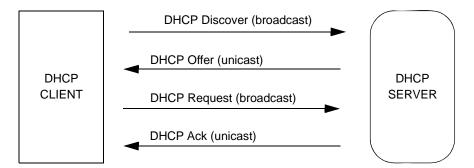

| 6.2.2.1   | DHCP Client                                                      | 6-15  |

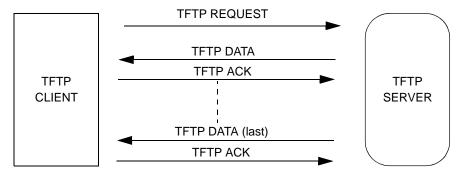

| 6.2.2.2   | TFTP Client                                                      | 6-16  |

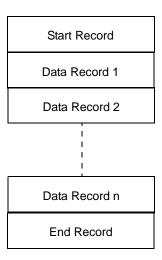

| 6.2.2.3   | Boot File Format                                                 |       |

| 6.2.3     | Simple Ethernet Boot                                             | 6-19  |

| 6.2.3.1   | Simple Ethernet Boot Flow                                        | 6-19  |

| 6.2.3.2   | Simple Ethernet Boot Ports                                       | 6-19  |

| 6.2.3.3   | Boot File Format                                                 | 6-20  |

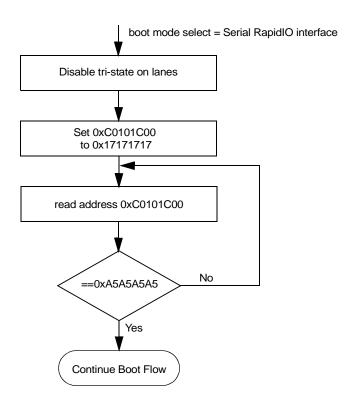

| 6.2.4     | Serial RapidIO Interconnect                                      | 6-21  |

| 6.2.4.1   | Serial RapidIO Without I <sup>2</sup> C Support                  | 6-21  |

| 6.2.4.2   | Serial RapidIO Interface with I2C Support                        | 6-22  |

| 6.2.5     | SPI                                                              | 6-22  |

| 6.3       | Jump to User Code                                                | 6-22  |

| 6.4       | System after Boot                                                | 6-23  |

| 6.5       | Boot Errors                                                      | 6-23  |

Freescale Semiconductor ix

ents

| 7      | Clocks                                                                |

|--------|-----------------------------------------------------------------------|

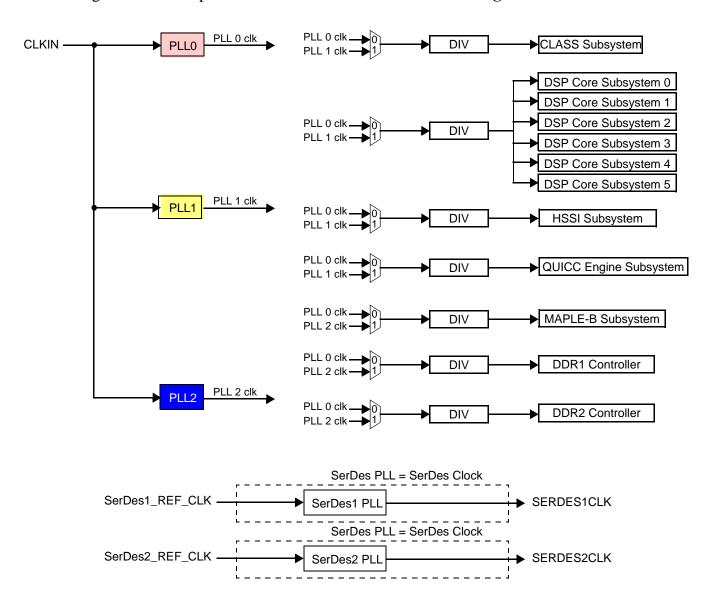

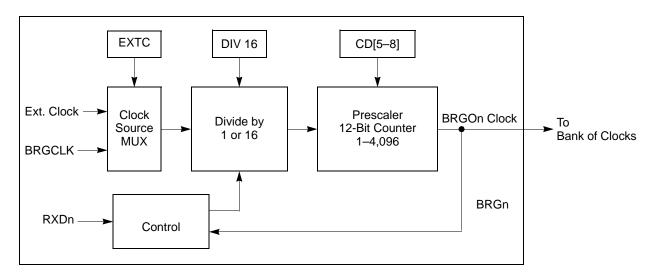

| 7.1    | Clock Generation Components and Modes                                 |

| 7.2    | .Programming Model                                                    |

| 7.2.1  | System Clock Control Register (SCCR)                                  |

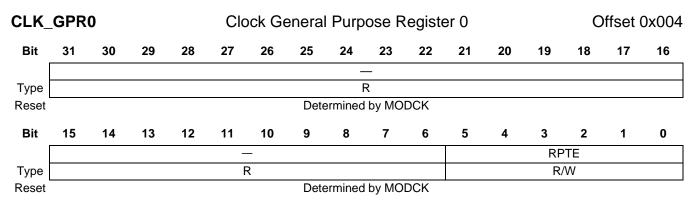

| 7.2.2  | Clock General Purpose Register 0 (CLK_GPR0)                           |

| 8      | General Configuration Registers                                       |

| 8.1    | Programming Model                                                     |

| 8.2    | Detailed Register Descriptions                                        |

| 8.2.1  | General Configuration Register 1 (GCR1) 8-2                           |

| 8.2.2  | General Configuration Register 2 (GCR2) 8-3                           |

| 8.2.3  | General Status Register 1 (GSR1)8-5                                   |

| 8.2.4  | High Speed Serial Interface Status Register (HSSI_SR) 8-7             |

| 8.2.5  | DDR General Control Register (DDR_GCR)8-10                            |

| 8.2.6  | High Speed Serial Interface Control Register 1 (HSSI_CR1) 8-12        |

| 8.2.7  | High Speed Serial Interface Control Register 2 (HSSI_CR2) 8-15        |

| 8.2.8  | QUICC Engine Control Register (QECR) 8-16                             |

| 8.2.9  | GPIO Pull-Up Enable Register (GPUER)8-17                              |

| 8.2.10 | GPIO Input Enable Register (GIER)8-18                                 |

| 8.2.11 | System Part and Revision ID Register (SPRIDR)                         |

| 8.2.12 | General Control Register 4 (GCR4)                                     |

| 8.2.13 | General Control Register 5 (GCR5) 8-22                                |

| 8.2.14 | General Status Register 2 (GSR2)8-24                                  |

| 8.2.15 | Core Subsystem Slave Port Priority Control Register (TSPPCR) 8-26     |

| 8.2.16 | QUICC Engine First External Request Multiplex Register (CPCE1R) 8-27  |

| 8.2.17 | QUICC Engine Second External Request Multiplex Register (CPCE2R) 8-28 |

| 8.2.18 | QUICC Engine Third External Request Multiplex Register (CPCE3R) 8-29  |

| 8.2.19 | QUICC Engine Fourth External Request Multiplex Register (CPCE4R) 8-30 |

| 8.2.20 | General Control Register 10 (GCR10)                                   |

| 8.2.21 | General Interrupt Register 1 (GIR1)                                   |

| 8.2.22 | General Interrupt Enable Register 1 (GIER1_x)8-35                     |

| 8.2.23 | General Interrupt Register 3 (GIR3)                                   |

| 8.2.24 | General Interrupt Enable Register 3 for Cores 0–3 (GIER3_x) 8-39      |

| 8.2.25 | General Interrupt Register 5 (GIR5)                                   |

| 8.2.26 | General Interrupt Enable Register 5 (GIER5_x)8-42                     |

| 8.2.27 | General Control Register 11 (GCR11)                                   |

| 8.2.28 | General Control Register 12 (GCR12)                                   |

| 8.2.29 | DMA Request0 Control Register (GCR_DREQ0)8-46                         |

| 8.2.30 | DMA Request1 Control Register (GCR_DREQ1)8-50                         |

| 8.2.31 | DMA Done Control Register (GCR_DDONE) 8-54                            |

| 8.2.32 | DDR1 General Configuration Register (DDR1_GCR)8-57                    |

x Freescale Semiconductor

| 8.2.33    | DDR2 General Configuration Register (DDR2_GCR)           | 8-58  |

|-----------|----------------------------------------------------------|-------|

| 8.2.34    | Core Subsystem Slave Port General Configuration Register |       |

|           | (CORE_SLV_GCR)                                           | 8-59  |

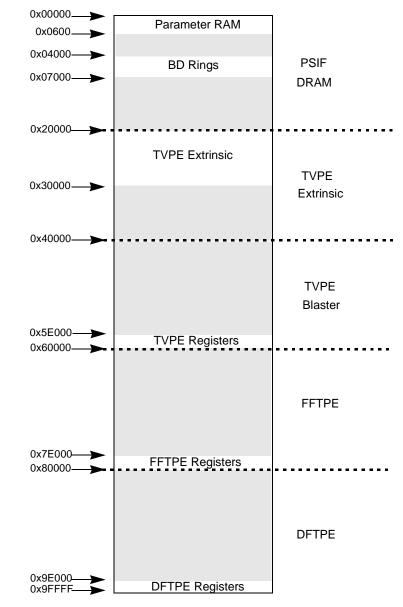

| 9         | Memory Map                                               |       |

| 9.1       | Shared Memory Address Space                              | 9-1   |

| 9.2       | Shared SC3850 DSP Core Subsystem M2/L2 Memories          |       |

| 9.3       | SC3850 DSP Core Subsystem Internal Address Space         |       |

| 9.4       | CCSR Address Space                                       |       |

| 9.5       | Initiators Views of the System Address Space             |       |

| 9.5.1     | SC3850 (Data) View of the System Address Space           |       |

| 9.5.2     | Peripherals View of the System Address Space             |       |

| 9.6       | Detailed System Memory Map                               |       |

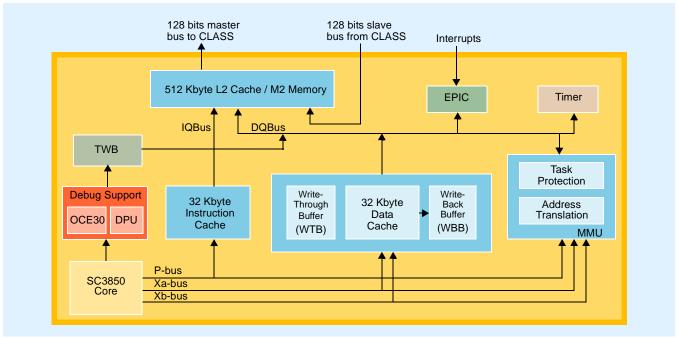

| 10        | MSC8156 SC3850 DSP Subsystem                             |       |

| 10.1      | SC3850 DSP Core Subsystem Features                       | 10-2  |

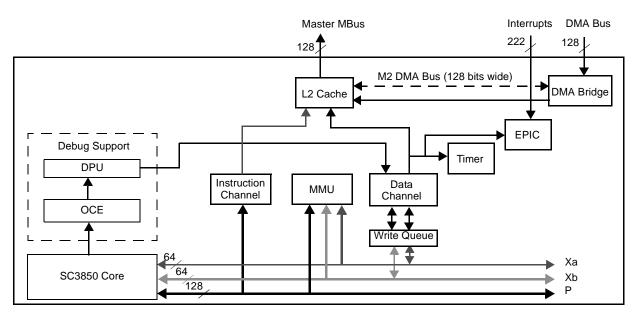

| 10.2      | SC3850 Core                                              |       |

| 10.3      | Instruction Channel                                      |       |

| 10.3.1    | Instruction Cache                                        |       |

| 10.3.2    | Instruction Fetch Unit                                   |       |

| 10.4      | Data Channel                                             |       |

| 10.4.1    | Data Cache                                               |       |

| 10.4.2    | Data Fetch Unit                                          |       |

| 10.4.3    | Write-Back Buffer                                        |       |

| 10.4.4    | Write-Through Buffer                                     |       |

| 10.4.5    | Data Control Unit                                        | 10-7  |

| 10.4.6    | Write Queue                                              | 10-8  |

| 10.5      | Memory Management Unit (MMU)                             | 10-8  |

| 10.6      | L2 Cache                                                 | 10-9  |

| 10.7      | On-Chip Emulator and Debug and Profiling Unit            | 10-10 |

| 10.8      | Extended Programmable Interrupt Controller               | 10-11 |

| 10.9      | Timer                                                    | 10-11 |

| 10.10     | Interfaces                                               | 10-11 |

| 10.10.1   | QBus to MBus Interface Bridge                            | 10-11 |

| 10.10.2   | MBus to DMA Bridge                                       | 10-11 |

| 10.11     | Entering and Exiting Wait and Stop States Safely         | 10-12 |

| 10.11.1   | Wait State                                               |       |

| 10.11.2   | Stop State                                               |       |

| 10.11.2.1 | Procedure for Entering DSP Subsystem Stop State Safely   |       |

| 10.11.2.2 | Procedure for Exiting the Stop State Safely              | 10-13 |

Freescale Semiconductor xi

| 11       | Internal Memory Subsystem                                   |        |

|----------|-------------------------------------------------------------|--------|

| 11.1     | Memory Management Unit (MMU)                                | . 11-2 |

| 11.2     | Instruction Channel (ICache and IFU)                        | . 11-3 |

| 11.3     | Data Channel and Write Queue (DCache)                       | . 11-5 |

| 11.4     | L2 Unified Cache/M2 Memory                                  | . 11-8 |

| 11.5     | M3 Memory                                                   | 11-12  |

| 11.6     | Internal Boot ROM                                           | 11-12  |

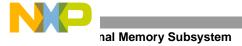

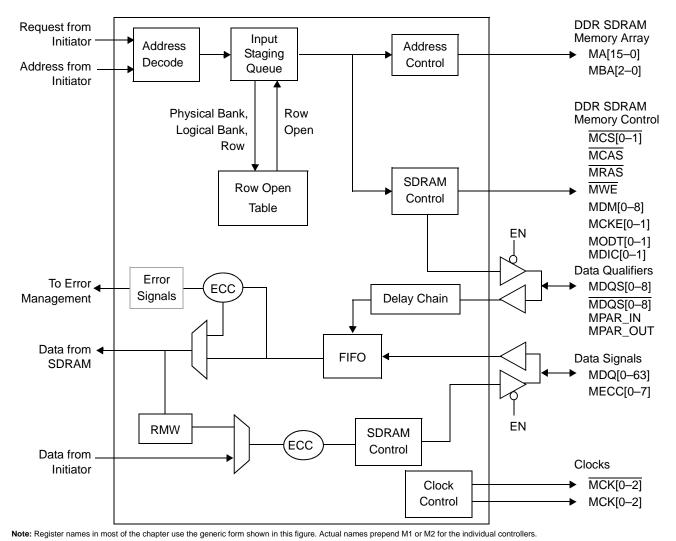

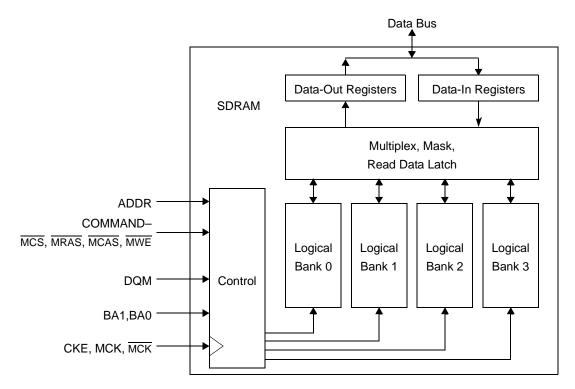

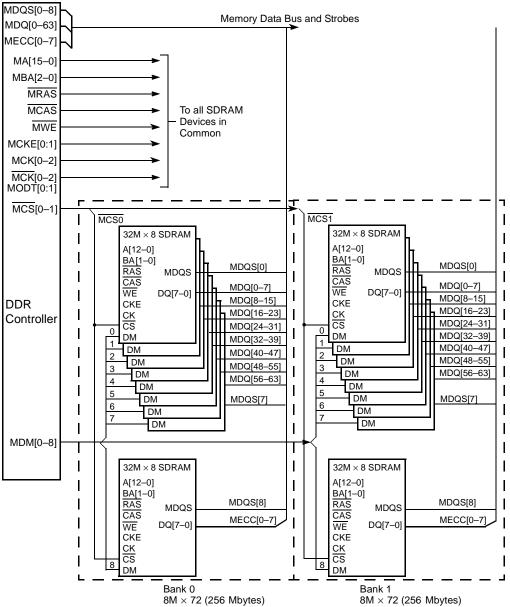

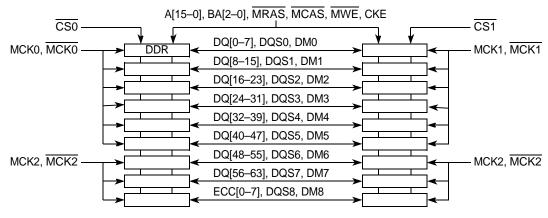

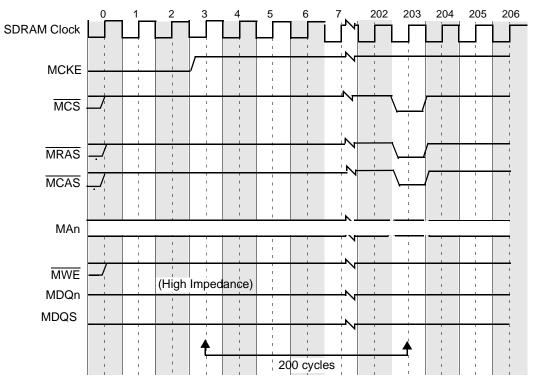

| 12       | DDR SDRAM Memory Controller                                 |        |

| 12.1     | Features                                                    | . 12-2 |

| 12.2     | Functional Description                                      |        |

| 12.2.1   | DDR SDRAM Interface Operation                               |        |

| 12.2.2   | DDR SDRAM Organization                                      |        |

| 12.2.3   | DDR SDRAM Address Multiplexing                              |        |

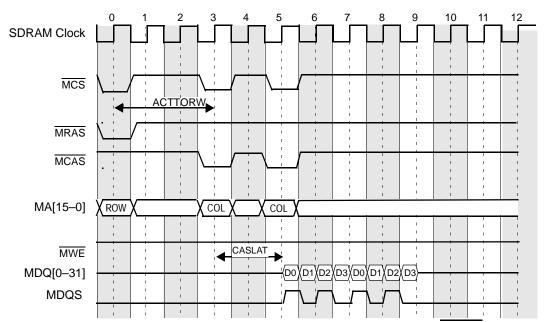

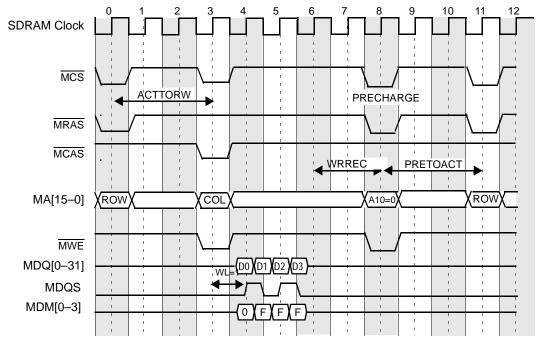

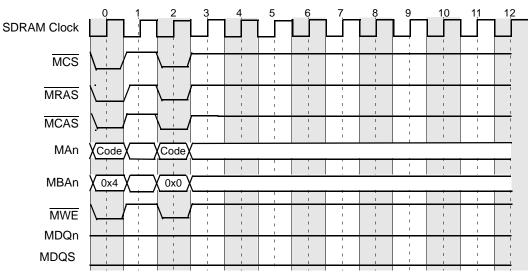

| 12.3     | JEDEC Standard DDR SDRAM Interface Commands                 |        |

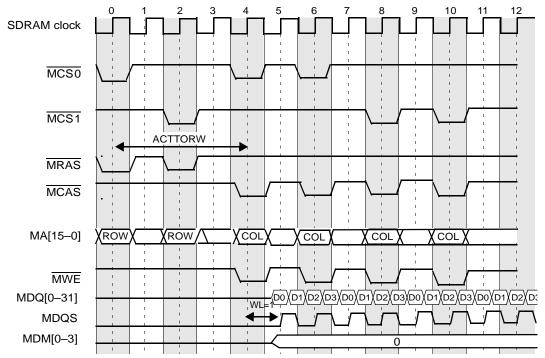

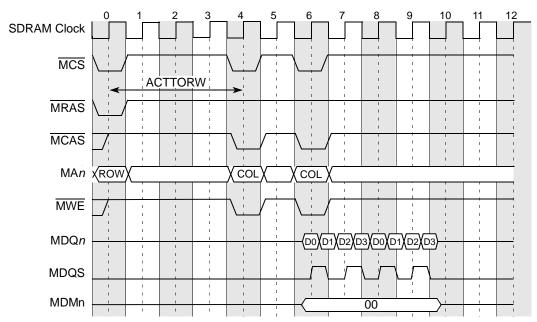

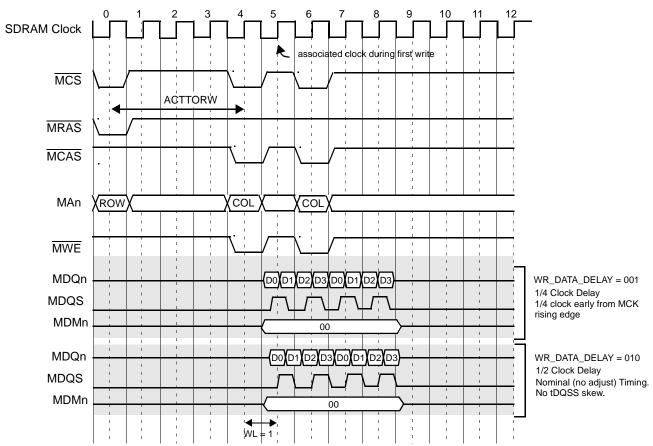

| 12.4     | DDR SDRAM Clocking and Interface Timing                     |        |

| 12.4.1   | Clock Distribution                                          |        |

| 12.4.2   | DDR SDRAM Mode-Set Command Timing                           |        |

| 12.4.3   | DDR SDRAM Registered DIMM Mode                              |        |

| 12.4.4   | DDR SDRAM Write Timing Adjustments                          |        |

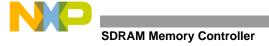

| 12.4.5   | DDR SDRAM Refresh                                           |        |

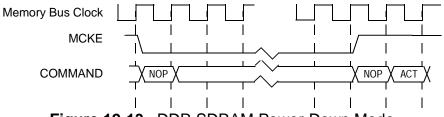

| 12.4.5.1 | DDR SDRAM Refresh Timing                                    |        |

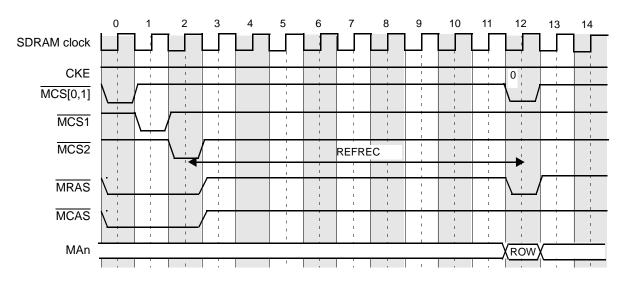

| 12.4.5.2 | DDR SDRAM Refresh and Power-Saving Modes                    |        |

| 12.4.6   | DDR Data Beat Ordering                                      |        |

| 12.4.7   | Page Mode and Logical Bank Retention                        | 12-32  |

| 12.5     | Error Checking and Correction                               | 12-32  |

| 12.6     | Error Management                                            |        |

| 12.7     | Set-Up and Initialization                                   | 12-36  |

| 12.7.1   | Programming Differences Between Memory Types                | 12-40  |

| 12.7.2   | DDR SDRAM Initialization Sequence                           | 12-44  |

| 12.8     | Memory Controller Programming Model                         | 12-44  |

| 12.8.1   | Chip-Select Bounds (MnCSx_BNDS)                             | 12-46  |

| 12.8.2   | Chip-Select x Configuration Register (MnCSx_CONFIG)         | 12-47  |

| 12.8.3   | Chip-Select x Configuration Register 2 (MnCSx_CONFIG_2)     | 12-49  |

| 12.8.4   | DDR SDRAM Timing Configuration 3 (MnTIMING_CFG_3)           | 12-50  |

| 12.8.5   | DDR SDRAM Timing Configuration Register 0 (MnTIMING_CFG_0)  | 12-52  |

| 12.8.6   | DDR SDRAM Timing Configuration Register 1 (MnTIMING_CFG_1)  | 12-55  |

| 12.8.7   | DDR SDRAM Timing Configuration Register 2 (MnTIMING_CFG_2)  | 12-60  |

| 12.8.8   | DDR SDRAM Control Configuration Register (MnDDR_SDRAM_CFG). | 12-65  |

| 12.8.9   | DDR SDRAM Control Configuration Register 2                  |        |

|          | (Madde SDRAM CEC 2)                                         | 12 67  |

xii Freescale Semiconductor

| 12.8.10 | DDR SDRAM Mode Configuration Register (MnDDR_SDRAM_MODE)      | 12-70 |

|---------|---------------------------------------------------------------|-------|

| 12.8.11 | DDR SDRAM Mode Configuration 2 Register                       |       |

|         | (MnDDR_SDRAM_MODE_2)                                          | 12-71 |

| 12.8.12 | DDR SDRAM Mode Control Register (MnDDR_SDRAM_MD_CNTL)         | 12-71 |

| 12.8.13 | DDR SDRAM Interval Configuration Register                     |       |

|         | (MnDDR_SDRAM_INTERVAL)                                        | 12-74 |

| 12.8.14 | DDR SDRAM Data Initialization Register (MnDDR_DATA_INIT)      | 12-75 |

| 12.8.15 | DDR SDRAM Clock Control Configuration Register                |       |

|         | (MnDDR_SDRAM_CLK_CNTL)                                        | 12-75 |

| 12.8.16 | DDR SDRAM Initialization Address Register (MnDDR_INIT_ADDR)   | 12-76 |

| 12.8.17 | DDR Initialization Enable (MnDDR_INIT_EN)                     |       |

| 12.8.18 | DDR SDRAM Timing Configuration 4 (MnTIMING_CFG_4)             | 12-78 |

| 12.8.19 | DDR SDRAM Timing Configuration 5 (MnTIMING_CFG_5)             | 12-80 |

| 12.8.20 | DDR ZQ Calibration Control (MnDDR_ZQ_CNTL)                    |       |

| 12.8.21 | DDR Write Leveling Control (MnDDR_WRLVL_CNTL)                 | 12-84 |

| 12.8.22 | DDR Write Leveling Control 2 (MnDDR_WRLVL_CNTL_2)             | 12-87 |

| 12.8.23 | DDR Write Leveling Control 3 (MnDDR_WRLVL_CNTL_3)             | 12-90 |

| 12.8.24 | DDR Pre-Drive Conditioning Control (MnDDR_PD_CNTL)            | 12-93 |

| 12.8.25 | DDR Self Refresh Counter (MnDDR_SR_CNTR)                      | 12-96 |

| 12.8.26 | DDR SDRAM Register Control Words 1 (MnDDR_SDRAM_RCW_1)        | 12-97 |

| 12.8.27 | DDR SDRAM Register Control Words 2 (MnDDR_SDRAM_RCW_2)        | 12-98 |

| 12.8.28 | DDR Debug Status Register 1 (MnDDRDSR_1)                      | 12-99 |

| 12.8.29 | DDR Debug Status Register 2 (MnDDRDSR_2)                      | 2-100 |

| 12.8.30 | DDR Control Driver Register 1 (MnDDRCDR_1)                    | 2-100 |

| 12.8.31 | DDR Control Driver Register 2 (MnDDRCDR_2)                    | 2-104 |

| 12.8.32 | DDR SDRAM IP Block Revision 1 Register (MnDDR_IP_REV1) 1      | 2-105 |

| 12.8.33 | DDR SDRAM IP Block Revision 2 Register (MnDDR_IP_REV2) 1      | 2-105 |

| 12.8.34 | DDR SDRAM Memory Data Path Error Injection Mask High Register |       |

|         | (MnDATA_ERR_INJECT_HI) 1                                      | 2-106 |

| 12.8.35 | DDR SDRAM Memory Data Path Error Injection Mask Low Register  |       |

|         | (MnDATA_ERR_INJECT_LO)                                        | 2-106 |

| 12.8.36 | DDR SDRAM Memory Data Path Error Injection Mask ECC Register  |       |

|         | (MnERR_INJECT)                                                | 2-107 |

| 12.8.37 | DDR SDRAM Memory Data Path Read Capture Data High Register    |       |

|         | (MnCAPTURE_DATA_HI)1                                          | 2-108 |

| 12.8.38 | DDR SDRAM Memory Data Path Read Capture Data Low Register     |       |

|         | (MnCAPTURE_DATA_LO) 1                                         | 2-108 |

| 12.8.39 | DDR SDRAM Memory Data Path Read Capture ECC Register          |       |

|         | (MnCAPTURE_ECC)                                               |       |

| 12.8.40 | DDR SDRAM Memory Error Detect Register (MnERR_DETECT) 1       |       |

| 12.8.41 | DDR SDRAM Memory Error Disable Register (MnERR_DISABLE) 1     | 2-110 |

|         |                                                               |       |

Freescale Semiconductor xiii

| 12.8.42  | DDR SDRAM Memory Error Interrupt Enable Register          |        |

|----------|-----------------------------------------------------------|--------|

|          | (MnERR_INT_EN)                                            | 12-112 |

| 12.8.43  | DDR SDRAM Memory Error Attributes Capture Register        |        |

|          | (MnCAPTURE_ATTRIBUTES)                                    | 12-113 |

| 12.8.44  | DDR SDRAM Memory Error Address Capture Register           |        |

|          | (MnCAPTURE_ADDRESS)                                       |        |

| 12.8.45  | DDR SDRAM Single-Bit ECC Memory Error Management Register |        |

|          | (MnERR_SBE)                                               |        |

| 12.8.46  | Debug Register 2 (MnDEBUG_2)                              | 12-115 |

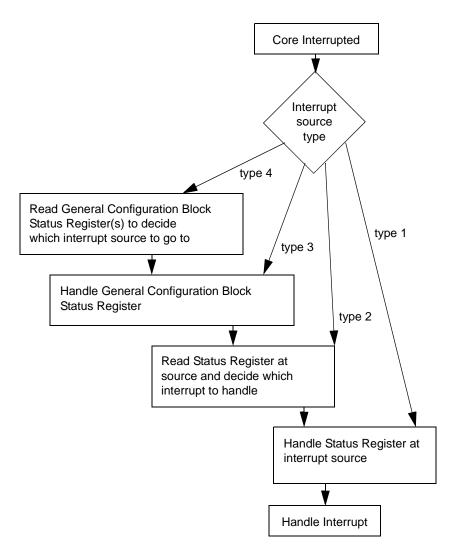

| 13       | Interrupt Handling                                        |        |

| 13.1     | Global Interrupt Controller (GIC)                         | 13-2   |

| 13.2     | General Configuration Block                               |        |

| 13.2.1   | Interrupt Groups                                          |        |

| 13.2.1   | External Interrupts                                       |        |

| 13.2.3   | Interrupt Handling                                        |        |

| 13.2.3   | Interrupt Mapping                                         |        |

| 13.4     | Core Interrupt Mesh                                       |        |

| 13.5     | Programming Model                                         |        |

| 13.5.1   | Global Interrupt Controller                               |        |

| 13.5.1.1 | Virtual Interrupt Generation Register (VIGR)              |        |

| 13.5.1.2 | Virtual Interrupt Status Register (VISR)                  |        |

| 13.5.2   | General Interrupt Configuration                           |        |

| 13.5.3   | Programming Restrictions                                  |        |

|          | Trogramming resuredons                                    | 15 20  |

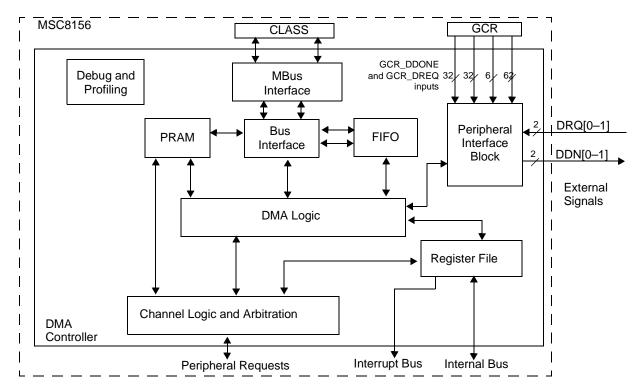

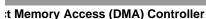

| 14       | Direct Memory Access (DMA) Controller                     |        |

| 14.1     | Operating Modes                                           | 14-2   |

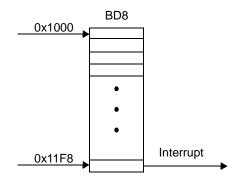

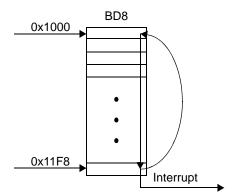

| 14.2     | Buffer Types                                              | 14-2   |

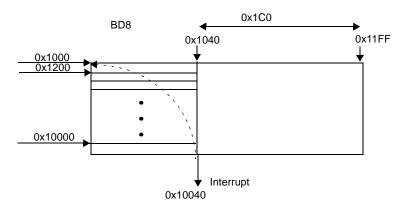

| 14.2.1   | One-Dimensional Simple Buffer                             |        |

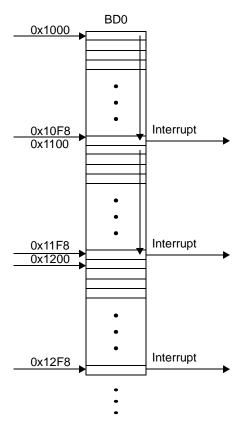

| 14.2.2   | One-Dimensional Cyclic Buffer                             | 14-5   |

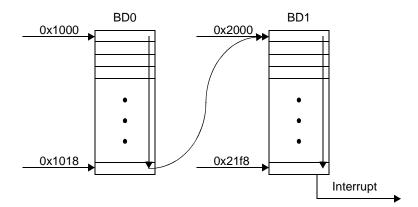

| 14.2.3   | One-Dimensional Chained Buffer                            | 14-6   |

| 14.2.4   | One-Dimensional Incremental Buffer                        | 14-7   |

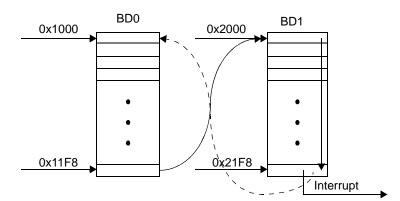

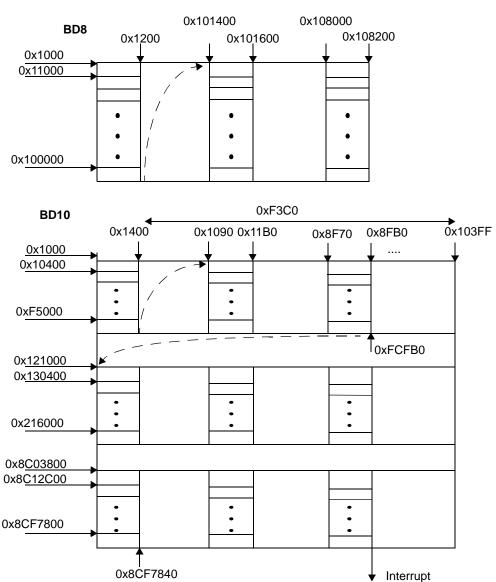

| 14.2.5   | One-Dimensional Complex Buffers With Dual Cyclic Buffers  | 14-8   |

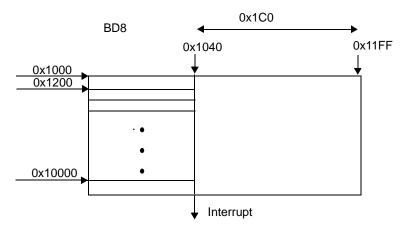

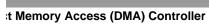

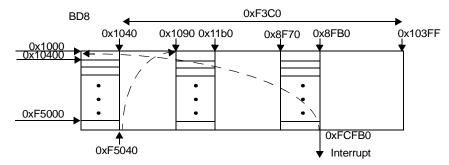

| 14.2.6   | Two-Dimensional Simple Buffer                             | 14-9   |

| 14.2.7   | Three-Dimensional Simple Buffer                           | 14-11  |

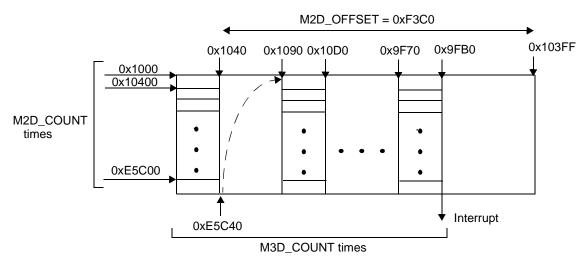

| 14.2.8   | Four-Dimensional Simple Buffer                            | 14-12  |

| 14.2.9   | Multi-Dimensional Chained Buffer                          | 14-15  |

| 14.2.10  | Two-Dimensional Cyclic Buffer                             | 14-17  |

| 14.2.11  | Three-Dimensional Cyclic Buffer                           | 14-18  |

| 14.3     | Arbitration Types                                         | 14-19  |

| 14.3.1   | Round-Robin Arbitration                                   | 14-19  |

xiv Freescale Semiconductor

14.7.22.2

|           |                                                              | Contents |

|-----------|--------------------------------------------------------------|----------|

| 14.3.2    | EDF Arbitration                                              | 14-20    |

| 14.3.2.1  | Issuing Interrupts                                           | 14-21    |

| 14.3.2.2  | Counter Control                                              | 14-21    |

| 14.3.2.3  | Clock Source to the Counters                                 | 14-22    |

| 14.4      | Interrupts                                                   | 14-22    |

| 14.4.1    | Maskable Interrupts                                          |          |

| 14.4.2    | Nonmaskable Interrupts                                       |          |

| 14.5      | Profiling                                                    |          |

| 14.6      | DMA Peripheral Interface                                     | 14-23    |

| 14.6.1    | Modes of Operation                                           |          |

| 14.6.2    | Configuration and Control Registers                          | 14-24    |

| 14.6.3    | Functional Description                                       |          |

| 14.6.3.1  | Request Signal                                               |          |

| 14.6.3.2  | Done Signal                                                  |          |

| 14.6.3.3  | Signal Operation                                             | 14-25    |

| 14.6.4    | Using the DMA Peripheral Interface Block                     |          |

| 14.7      | DMA Programming Model                                        |          |

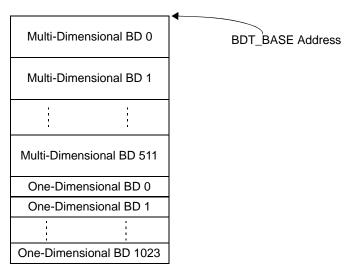

| 14.7.1    | DMA Buffer Descriptor Base Registers x (DMABDBRx)            | 14-28    |

| 14.7.2    | DMA Controller Channel Configuration Registers x (DMACHCRx)  |          |

| 14.7.3    | DMA Controller Global Configuration Register (DMAGCR)        |          |

| 14.7.4    | DMA Channel Enable Register (DMACHER)                        |          |

| 14.7.5    | DMA Channel Disable Register (DMACHDR)                       |          |

| 14.7.6    | DMA Channel Freeze Register (DMACHFR)                        | 14-33    |

| 14.7.7    | DMA Channel Defrost Register (DMACHDFR)                      | 14-33    |

| 14.7.8    | DMA Time-To-Dead Line Registers x (DMAEDFTDLx)               | 14-34    |

| 14.7.9    | DMA EDF Control Register (DMAEDFCTRL)                        | 14-35    |

| 14.7.10   | DMA EDF Mask Register (DMAEDFMR)                             | 14-35    |

| 14.7.11   | DMA EDF Mask Update Register (DMAEDFMUR)                     | 14-36    |

| 14.7.12   | DMA EDF Status Register (DMAEDFSTR)                          | 14-38    |

| 14.7.13   | DMA Mask Register (DMAMR)                                    | 14-38    |

| 14.7.14   | DMA Mask Update Register (DMAMUR)                            |          |

| 14.7.15   | DMA Status Register (DMASTR)                                 | 14-40    |

| 14.7.16   | DMA Error Register (DMAERR)                                  | 14-41    |

| 14.7.17   | DMA Debug Event Status Register (DMADESR)                    | 14-43    |

| 14.7.18   | DMA Local Profiling Configuration Register (DMALPCR)         |          |

| 14.7.19   | DMA Round-Robin Priority Group Update Register (DMARRPGUR) . | 14-44    |

| 14.7.20   | DMA Channel Active Status Register (DMACHASTR)               | 14-45    |

| 14.7.21   | DMA Channel Freeze Status Register (DMACHFSTR)               | 14-45    |

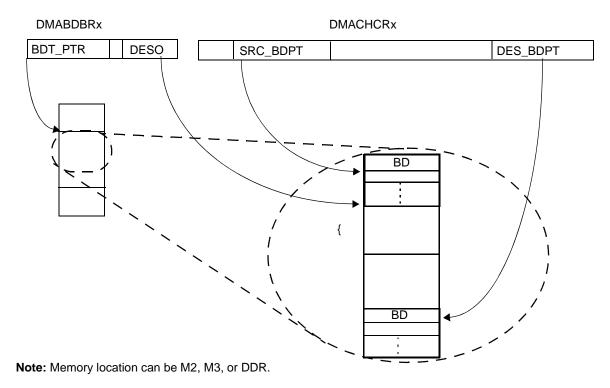

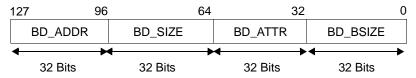

| 14.7.22   | DMA Channel Buffer Descriptors                               | 14-45    |

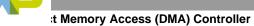

| 14.7.22.1 | Buffer Attributes (BD_ATTR)                                  | 14-49    |

MSC8156 Reference Manual, Rev. 2

Freescale Semiconductor  $\mathsf{X}\mathsf{V}$

Multi-Dimensional Buffer Attributes (BD\_MD\_ATTR)......14-52

#### ents

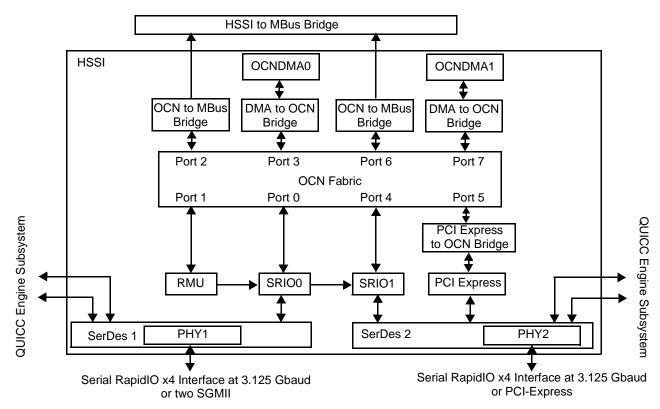

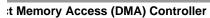

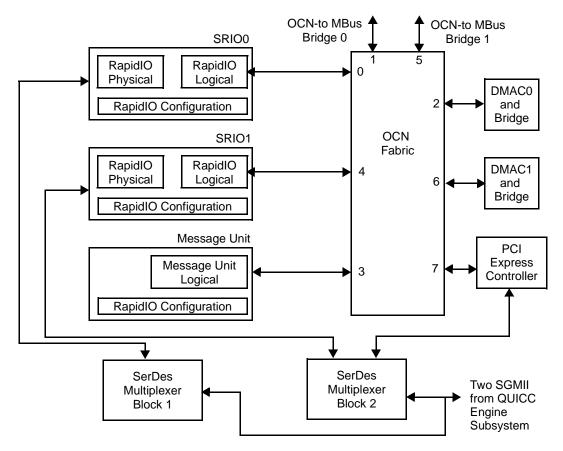

| <b>15</b>  | High Speed Serial Interface (HSSI) Subsystem                    |         |

|------------|-----------------------------------------------------------------|---------|

| 15.1       | HSSI Subsystem Block Diagram                                    | 15-2    |

| 15.2       | OCN Fabric                                                      | 15-3    |

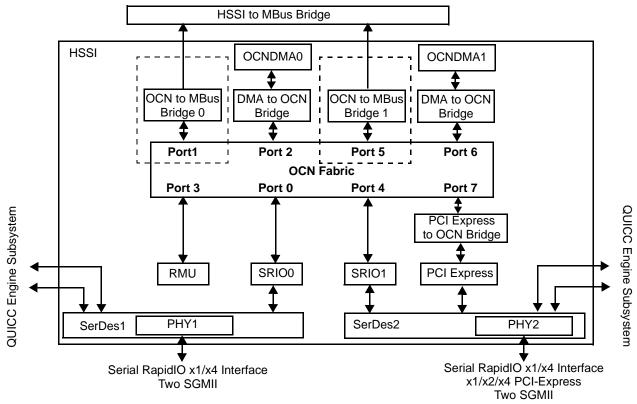

| 15.3       | DMA Controllers                                                 | 15-4    |

| 15.3.1     | Overview                                                        | 15-5    |

| 15.3.2     | Features                                                        | 15-5    |

| 15.3.3     | Modes of Operation                                              | 15-5    |

| 15.4       | Functional Description                                          | 15-7    |

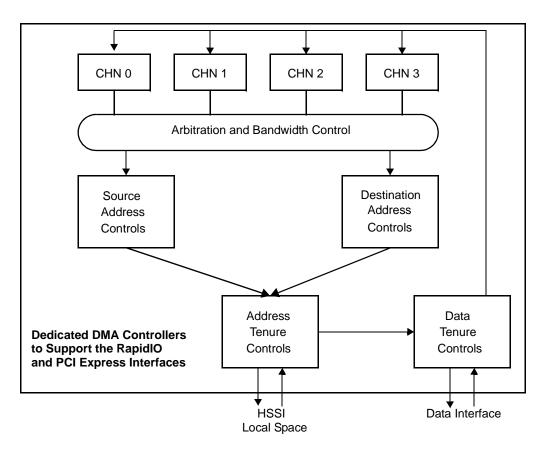

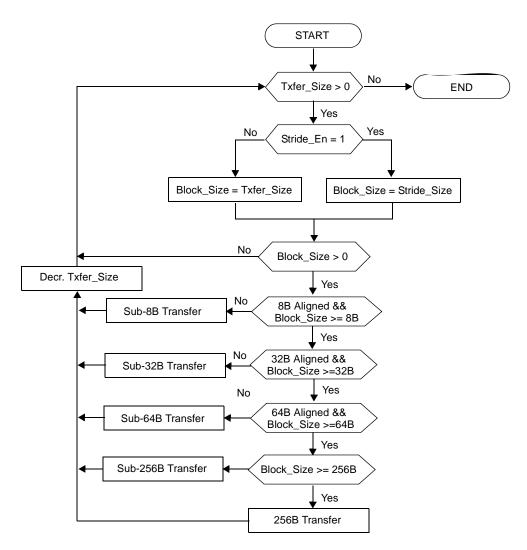

| 15.4.1     | DMA Channel Operation                                           |         |

| 15.4.1.1   | Source/Destination Transaction Size Calculations                | 15-7    |

| 15.4.1.2   | Basic DMA Mode Transfer                                         | 15-9    |

| 15.4.1.2.1 | Basic Direct Mode                                               | 15-9    |

| 15.4.1.2.2 | Basic Direct Single-Write Start Mode                            | . 15-10 |

| 15.4.1.2.3 | Basic Chaining Mode                                             |         |

| 15.4.1.2.4 | Basic Chaining Single-Write Start Mode                          | . 15-11 |

| 15.4.1.2.5 | Extended DMA Mode Transfer                                      |         |

| 15.4.1.3   | Channel Continue Mode for Cascading Transfer Chains             | . 15-13 |

| 15.4.1.3.1 | Basic Mode                                                      |         |

| 15.4.1.3.2 | Extended Mode                                                   | . 15-14 |

| 15.4.1.4   | Channel Abort                                                   | . 15-14 |

| 15.4.1.5   | Bandwidth Control                                               | . 15-15 |

| 15.4.1.6   | Channel State                                                   | . 15-15 |

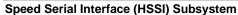

| 15.4.1.7   | Illustration of Stride Size and Stride Distance                 | . 15-15 |

| 15.4.2     | DMA Transfer Interfaces                                         | . 15-16 |

| 15.4.3     | DMA Errors                                                      | . 15-16 |

| 15.4.4     | DMA Descriptors                                                 | . 15-17 |

| 15.4.5     | Local Access ATMU Registers                                     | . 15-19 |

| 15.4.6     | Limitations and Restrictions                                    | . 15-19 |

| 15.5       | OCN-to-MBus (O2M) Bridges                                       | . 15-21 |

| 15.6       | SRIO Port Controller Modules (SRIOn)                            | . 15-21 |

| 15.7       | SerDes PHY Interfaces                                           | . 15-21 |

| 15.8       | HSSI Programming Model                                          | . 15-21 |

| 15.8.1     | Mode Registers 0–3 (DnMR[0–3])                                  | . 15-24 |

| 15.8.2     | Status Registers (DnSRn)                                        | . 15-27 |

| 15.8.3     | Current Link Descriptor Extended Address Registers (DnECLNDARn) | . 15-29 |

| 15.8.4     | Current Link Descriptor Address Registers (DnCLNDARn):          | . 15-30 |

| 15.8.5     | Source Attributes Registers (DnSATRn)                           | . 15-31 |

| 15.8.6     | Source Address Registers (DnSARn)                               |         |

| 15.8.7     | Destination Attributes Registers (DnDATRn)                      | . 15-33 |

| 15.8.8     | Destination Address Registers (DnDARn)                          | . 15-34 |

| 15 8 0     | Ryta Count Registers (DnRCPn)                                   | 15 35   |

MSC8156 Reference Manual, Rev. 2

xvi Freescale Semiconductor

| 15.8.10  | Extended Next Link Descriptor Address Registers (DnENLNDARn)    | . 15-36 |

|----------|-----------------------------------------------------------------|---------|

| 15.8.11  | Next Link Descriptor Address Registers (DnNLNDARn)              | . 15-37 |

| 15.8.12  | Extended Current List Descriptor Address Registers (DnECLSDARn) | . 15-38 |

| 15.8.13  | Current List Descriptor Address Registers (DnCLSDARn)           | . 15-39 |

| 15.8.14  | Extended Next List Descriptor Address Registers (DnENLSDARn)    | . 15-40 |

| 15.8.15  | Next List Descriptor Address Registers (DnNLSDARn)              | . 15-41 |

| 15.8.16  | Source Stride Registers (DnSSRn)                                | . 15-42 |

| 15.8.17  | Destination Stride Registers (DnDSRn)                           | . 15-43 |

| 15.8.18  | DMA General Status Register (DnDGSR))                           | . 15-44 |

| 15.8.19  | Local Access Window Base Address Registers 0–9 (DnLAWBAR[0–9])  | . 15-46 |

| 15.8.20  | Local Access Window Attributes Registers 0–9 (DnLAWAR[0–9])     | . 15-47 |

| 15.8.21  | OCN-to-MBus Configuration Registers (O2MCR[0–1])                | . 15-49 |

| 15.8.22  | OCN-to-MBus Error Attribute Registers (O2MEAR[0-1])             | . 15-50 |

| 15.8.23  | OCN-to-MBus Error Address Registers (O2MEADR[0-1])              | . 15-52 |

| 15.8.24  | OCN-to-MBus Error Status Registers (O2MESR[0-1])                | . 15-53 |

| 15.8.25  | OCN-to-MBus Interrupt Enable Registers (O2MIER[0–1])            | . 15-54 |

| 15.8.26  | OCN-to-MBus Error Capture Enable Registers (O2MECER[0-1])       | . 15-55 |

| 15.8.27  | SRDS Control Register 0 (SRDSnCR0)                              | . 15-56 |

| 15.8.28  | SRDS Control Register 1 (SRDSnCR1)                              | . 15-59 |

| 15.8.29  | SRDS Control Register 2 (SRDSnCR2)                              | . 15-62 |

| 15.8.30  | SRDS Control Register 3 (SRDSnCR3)                              | . 15-63 |

| 15.8.31  | SRDS Control Register 4 (SRDSnCR4)                              | . 15-65 |

| 15.8.32  | SRDS Control Register 5 (SRDSnCR5)                              | . 15-67 |

| 15.8.33  | SRDS Control Register 6 (SRDSnCR6)                              | . 15-68 |

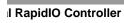

| 16       | Serial RapidIO Controller                                       |         |

| 16.1     | Introduction                                                    | 16-3    |

| 16.1.1   | Features                                                        |         |

| 16.1.2   | Operating Modes                                                 |         |

| 16.1.3   | 1x/4x LP-Serial Signals                                         |         |

| 16.1.4   | RapidIO Interface Activation                                    |         |

| 16.1.4.1 | Initialization for Booting the MSC8156 DSP                      | 16-6    |

| 16.1.4.2 | Initialization for Non-Boot Operation                           | 16-6    |

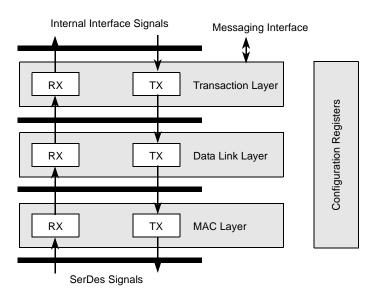

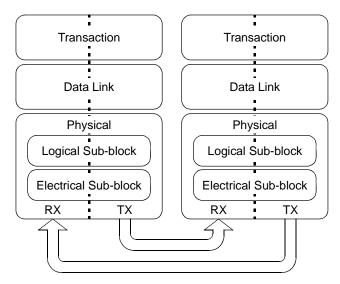

| 16.2     | RapidIO Interface Basics                                        | 16-6    |

| 16.2.1   | RapidIO Transactions                                            | 16-7    |

| 16.2.2   | RapidIO Packet Format                                           | 16-8    |

| 16.2.3   | RapidIO Control Symbol Summary                                  | 16-9    |

| 16.2.4   | Accessing Configuration Registers via RapidIO Packets           | . 16-11 |

| 16.2.4.1 | Inbound Maintenance Accesses                                    |         |

| 16.2.4.2 | RapidIO Non-Maintenance Accesses Using LCSBA1CSR                | . 16-12 |

| 16.2.4.3 | RapidIO Maintenance Accesses                                    | . 16-12 |

MSC8156 Reference Manual, Rev. 2

Freescale Semiconductor xvii

#### ents

| 16.2.4.3.1 | Guidelines                                        | 16-12  |

|------------|---------------------------------------------------|--------|

| 16.2.4.3.2 | Outbound Maintenance Accesses                     | 16-12  |

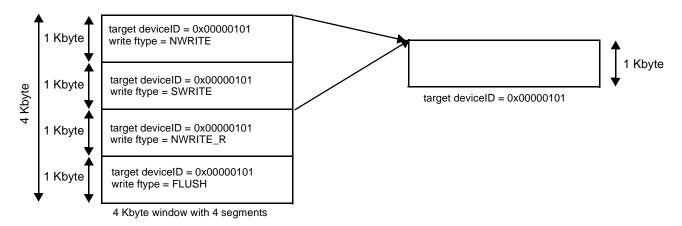

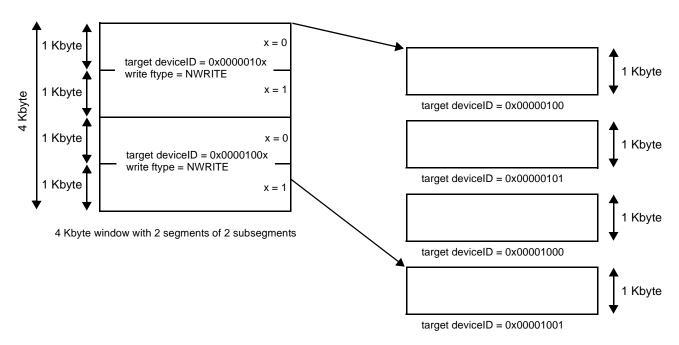

| 16.2.5     | RapidIO ATMU Implementation                       | 16-13  |

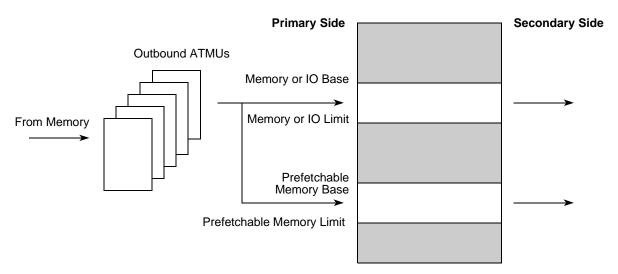

| 16.2.5.1   | RapidIO Outbound ATMU                             | 16-13  |

| 16.2.5.2   | Outbound Windows                                  | 16-15  |

| 16.2.5.3   | Window Size and Segmented Windows                 | 16-16  |

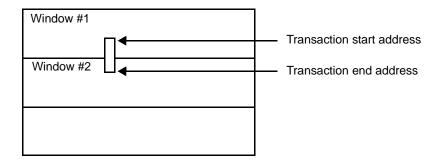

| 16.2.5.3.1 | Valid Hits to Multiple ATMU Windows               | 16-40  |

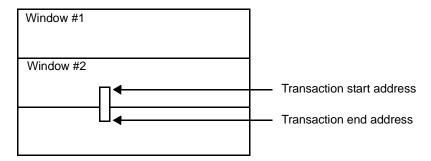

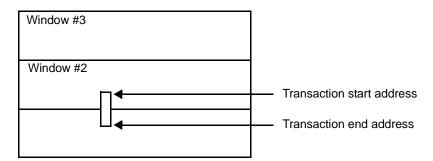

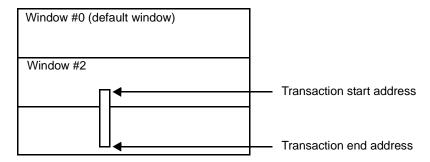

| 16.2.5.3.2 | Window Boundary Crossing Errors                   | 16-41  |

| 16.2.5.4   | RapidIO Inbound ATMU                              | 16-42  |

| 16.2.5.4.1 | Hits to Multiple ATMU Windows                     | 16-44  |

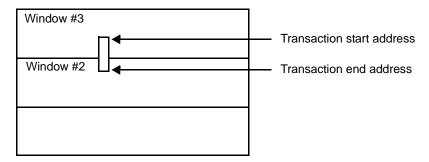

| 16.2.5.4.2 | Window Boundary Crossing Errors                   | 16-44  |

| 16.2.6     | Generating Link-Request/Reset-Device              | 16-45  |

| 16.2.7     | Outbound Drain Mode                               | 16-46  |

| 16.2.8     | Input Port Disable Mode                           | 16-47  |

| 16.2.9     | Software Assisted Error Recovery Register Support | 16-47  |

| 16.2.10    | Errors and Error Handling                         | 16-48  |

| 16.2.10.1  | RapidIO Error Description                         | 16-48  |

| 16.2.10.2  | Physical Layer RapidIO Errors                     | 16-50  |

| 16.2.10.3  | Logical Layer RapidIO Errors                      |        |

| 16.3       | RapidIO Message Unit                              | 16-79  |

| 16.3.1     | Features                                          | 16-79  |

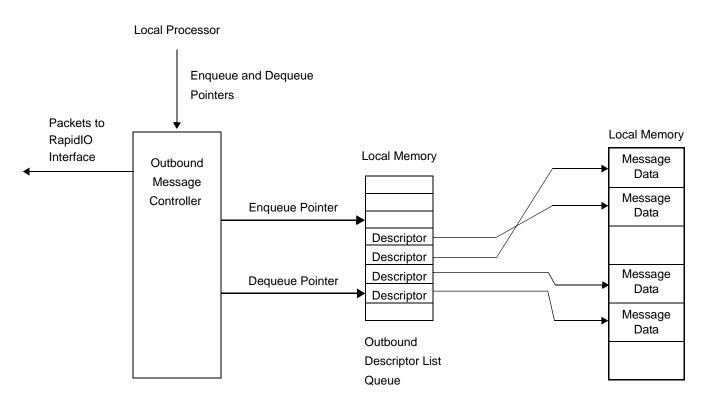

| 16.3.2     | Outbound Message Controller Operation             | 16-80  |

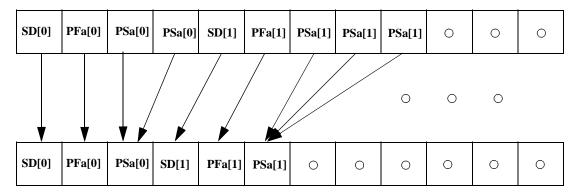

| 16.3.2.1   | Direct Mode                                       | 16-80  |

| 16.3.2.2   | Software Error Handling                           | 16-83  |

| 16.3.2.3   | Disabling and Enabling the Message Controller     | 16-84  |

| 16.3.2.4   | Hardware Error Handling                           | 16-84  |

| 16.3.2.5   | Chaining Mode                                     | 16-88  |

| 16.3.2.5.1 | Changing Descriptor Queues in Chaining Mode       | 16-91  |

| 16.3.2.5.2 | Preventing Queue Overflow in Chaining Mode        | 16-91  |

| 16.3.2.5.3 | Switching Between Direct and Chaining Modes       | 16-91  |

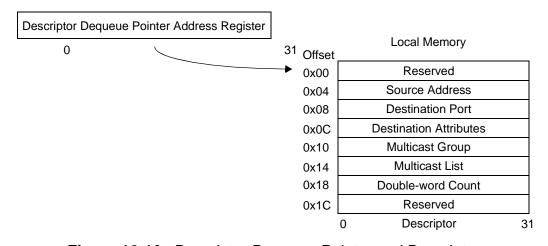

| 16.3.2.5.4 | Chaining Mode Descriptor Format                   | 16-92  |

| 16.3.2.5.5 | Chaining Mode Controller Interrupts               | 16-93  |

| 16.3.2.6   | Software Error Handling                           | 16-94  |

| 16.3.2.7   | Hardware Error Handling                           | 16-95  |

| 16.3.2.8   | Outbound Message Controller Arbitration           | 16-96  |

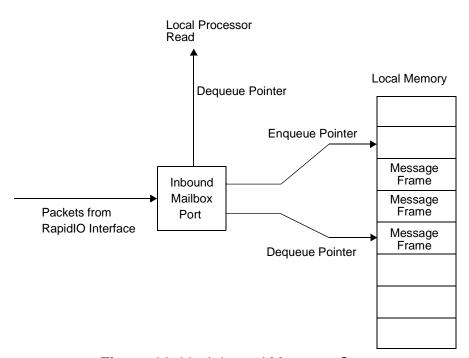

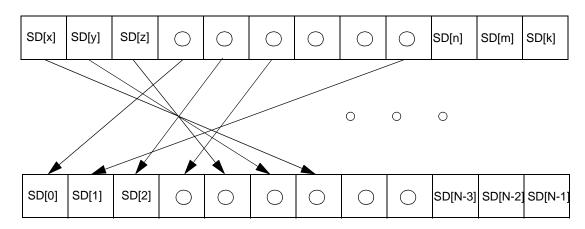

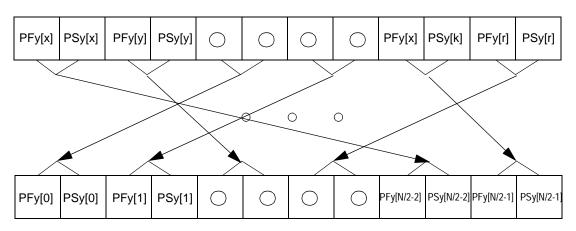

| 16.3.3     | Inbound Message Controller Operation              | 16-97  |

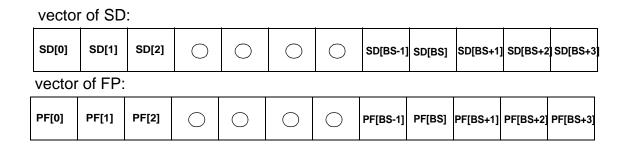

| 16.3.3.1   | Inbound Message Controller Initialization         |        |

| 16.3.3.2   | Inbound Controller Operation                      | 16-98  |

| 16.3.3.3   | Message Steering                                  | 16-100 |

| 16.3.3.4   | Retry Response Conditions                         |        |

| 16.3.3.5   | Inbound Message Controller Interrupts             | 16-100 |

MSC8156 Reference Manual, Rev. 2

xviii Freescale Semiconductor

| 16.3.3.6 | Software Error Handling                                     | 16-101 |

|----------|-------------------------------------------------------------|--------|

| 16.3.3.7 | Hardware Error Handling                                     | 16-102 |

| 16.3.3.8 | Programming Errors                                          | 16-107 |

| 16.3.3.9 | Disabling and Enabling the Inbound Message Controller       | 16-107 |

| 16.3.4   | RapidIO Message Passing Logical Specification Register Bits | 16-108 |

| 16.4     | RapidIO Doorbell                                            | 16-108 |

| 16.4.1   | Features                                                    | 16-108 |

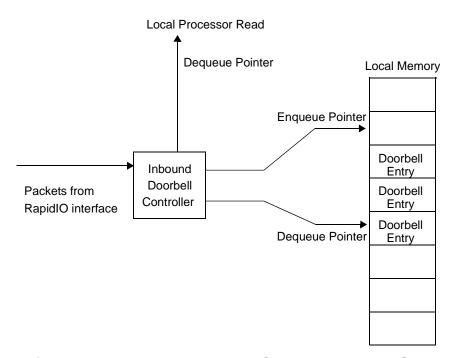

| 16.4.2   | Doorbell Controller                                         | 16-109 |

| 16.4.3   | Outbound Doorbell Controller                                | 16-110 |

| 16.4.3.1 | Interrupts                                                  | 16-111 |

| 16.4.3.2 | Software Error Handling                                     | 16-111 |

| 16.4.3.3 | Hardware Error Handling                                     | 16-112 |

| 16.4.3.4 | Programming Errors                                          | 16-114 |

| 16.4.4   | Inbound Doorbell Controller                                 | 16-115 |

| 16.4.4.1 | Doorbell Queue Entry Format                                 | 16-116 |

| 16.4.4.2 | Retry Response Conditions                                   | 16-117 |

| 16.4.4.3 | Doorbell Controller Interrupts                              | 16-117 |

| 16.4.4.4 | Transaction Errors                                          | 16-118 |

| 16.4.4.5 | Software Error Handling                                     | 16-118 |

| 16.4.4.6 | Hardware Error Handling                                     | 16-118 |

| 16.4.4.7 | Programming Errors                                          | 16-121 |

| 16.4.4.8 | Disabling and Enabling the Doorbell Controller              | 16-122 |

| 16.4.4.9 | RapidIO Message Passing Logical Specification Registers     | 16-122 |

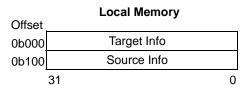

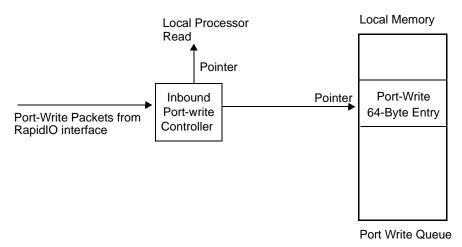

| 16.5     | Port-Write Controller                                       | 16-123 |

| 16.5.1   | Port-Write Controller Initialization                        | 16-123 |

| 16.5.2   | Port-Write Controller Operation                             | 16-124 |

| 16.5.3   | Port-Write Controller Interrupts                            | 16-124 |

| 16.5.4   | Discarding Port-Writes                                      | 16-125 |

| 16.5.5   | Transaction Errors                                          | 16-125 |

| 16.5.6   | Software Error Handling                                     | 16-125 |

| 16.5.7   | Hardware Error Handling                                     |        |

| 16.5.8   | Disabling and Enabling the Port-Write Controller            | 16-128 |

| 16.5.9   | RapidIO Message Passing Logical Specification Registers     | 16-129 |

| 16.6     | RapidIO Programming Model                                   |        |

| 16.6.1   | Device Identity Capability Register (DIDCAR)                | 16-133 |

| 16.6.2   | Device Information Capability Register (DICAR)              | 16-133 |

| 16.6.3   | Assembly Identity Capability Register (AIDCAR)              |        |

| 16.6.4   | Assembly Information Capability Register (AICAR)            |        |

| 16.6.5   | Processing Element Features Capability Register (PEFCAR)    |        |

| 16.6.6   | Source Operations Capability Register (SOCAR)               |        |

| 16.6.7   | Destination Operations Capability Register (DOCAR)          |        |

xix

Freescale Semiconductor

| _ | 'n | 4 | c |

|---|----|---|---|

| 16.6.8  | Mailbox Command and Status Register (MCSR)                                |

|---------|---------------------------------------------------------------------------|

| 16.6.9  | Port Write and Doorbell Command and Status Register (PWDCSR) 16-141       |

| 16.6.10 | Processing Element Logical Layer Control Command and Status Register      |

|         | (PELLCCSR)                                                                |

| 16.6.11 | Local Configuration Space Base Address 1 Command and Status               |

|         | Register (LCSBA1CSR)                                                      |

| 16.6.12 | Base Device ID Command and Status Register (BDIDCSR) 16-144               |

| 16.6.13 | Host Base Device ID Lock Command and Status Register                      |

|         | (HBDIDLCSR)                                                               |

| 16.6.14 | Component Tag Command and Status Register (CTCSR) 16-146                  |

| 16.6.15 | Port Maintenance Block Header 0 (PMBH0) 16-147                            |

| 16.6.16 | Port Link Time-Out Control Command and Status Register (PLTOCCSR) 16-148  |

| 16.6.17 | Port Response Time-Out Control Command and Status Register                |

|         | (PRTOCCSR)                                                                |

| 16.6.18 | Port General Control Command and Status Register (PGCCSR) 16-150          |

| 16.6.19 | Port 0–1 Link Maintenance Request Command and Status Register             |

|         | (PnLMREQCSR)                                                              |

| 16.6.20 | Port 0–1 Link Maintenance Response Command and Status Register            |

|         | (PnLMRESPCSR)                                                             |

| 16.6.21 | Port 0–1 Local ackID Command and Status Register (PnLASCR) 16-153         |

| 16.6.22 | Port 0–1 Error and Status Command and Status Register (PnESCSR) 16-154    |

| 16.6.23 | Port 0–1 Control Command and Status Register (PnCCSR) 16-156              |

| 16.6.24 | Error Reporting Block Header (ERBH)                                       |

| 16.6.25 | Logical/Transport Layer Error Detect Command and Status Register          |

|         | (LTLEDCSR)                                                                |

| 16.6.26 | Logical/Transport Layer Error Enable Command and Status Register          |

|         | (LTLEECSR) 16-160                                                         |

| 16.6.27 | Logical/Transport Layer Address Capture Command and Status Register       |

|         | (LTLACCSR)                                                                |

| 16.6.28 | Logical/Transport Layer Device ID Capture Command and Status Register     |

|         | (LTLDIDCCSR)                                                              |

| 16.6.29 | Logical/Transport Layer Control Capture Command and Status Register       |

|         | (LTLCCCSR)                                                                |

| 16.6.30 | Port 0–1 Error Detect Command and Status Register (PnEDCSR) 16-164        |

| 16.6.31 | Port 0–1 Error Rate Enable Command and Status Register (PnERECSR). 16-165 |

| 16.6.32 | Port 0–1 Error Capture Attributes Command and Status Register             |

|         | (PnECACSR)                                                                |

| 16.6.33 | Port 0–1 Packet/Control Symbol Error Capture Command and Status Register  |

| 16634   | (PnPCSECCSR)                                                              |

| 16.6.34 | Port 0–1 Packet Error Capture Command and Status Register 1               |

|         | (PnPECCSR1)                                                               |

xx Freescale Semiconductor

| 16.6.35 | Port 0–1 Packet Error Capture Command and Status Register 2                   |

|---------|-------------------------------------------------------------------------------|

|         | (PnPECCSR2)                                                                   |

| 16.6.36 | Port 0–1 Packet Error Capture Command and Status Register 3                   |

|         | (PnPECCSR3)                                                                   |

| 16.6.37 | Port 0–1 Error Rate Command and Status Register (PnERCSR) 16-172              |

| 16.6.38 | Port 0–1 Error Rate Threshold Command and Status Register                     |

|         | (PnERTCSR)                                                                    |

| 16.6.39 | Logical Layer Configuration Register (LLCR)                                   |

| 16.6.40 | Error/Port-Write Status Register (EPWISR)                                     |

| 16.6.41 | Logical Retry Error Threshold Configuration Register (LRETCR) 16-176          |

| 16.6.42 | Physical Retry Error Threshold Configuration Register (PRETCR) 16-177         |

| 16.6.43 | Port 0–1 Alternate Device ID Command and Status Register                      |

|         | (PnADIDCSR)                                                                   |

| 16.6.44 | Port 0–1 Pass-Through Accept-All Configuration Register (PnPTAACR) 16-179     |

| 16.6.45 | Port 0–1 Logical Outbound Packet Time-to-Live Configuration Register          |

|         | (PnLOPTTLCR)                                                                  |

| 16.6.46 | Port 0-1 Implementation Error Command and Status Register (PnIECSR) 16-181    |

| 16.6.47 | Port 0–1 Serial Link Command and Status Register (PnSLCSR) 16-182             |

| 16.6.48 | Port 0–1 Serial Link Error Injection Configuration Register (PnSLEICR) 16-183 |

| 16.6.49 | IP Block Revision Register 1 (IPBRR1)                                         |

| 16.6.50 | IP Block Revision Register 2 (IPBRR2)                                         |

| 16.6.51 | Port 0–1 RapidIO Outbound Window Translation Address Registers x              |

|         | (PnROWTARx)                                                                   |

| 16.6.52 | Port 0-1 RapidIO Outbound Window Translation Extended Address Registers x     |

|         | (PnROWTEARx)                                                                  |

| 16.6.53 | Port 0–1 RapidIO Outbound Window Base Address Registers x                     |

|         | (PnROWBARx)                                                                   |

| 16.6.54 | Port 0–1 RapidIO Outbound Window Attributes Registers x                       |

|         | (PnROWARx)                                                                    |

| 16.6.55 | Port 0–1 RapidIO Outbound Window Segment 1–3 Registers 1–8                    |

|         | (PnROWSxRy)                                                                   |

| 16.6.56 | Port 0–1 RapidIO Inbound Window Translation Address Registers x               |

|         | (PnRIWTARx)                                                                   |

| 16.6.57 | Port 0–1 RapidIO Inbound Window Base Address Registers x                      |

|         | (PnRIWBARx)                                                                   |

| 16.6.58 | Port 0–1 RapidIO Inbound Window Attributes Registers x (PnRIWARx) 16-193      |

| 16.6.59 | Outbound Message x Mode Registers (OMxMR) 16-194                              |

| 16.6.60 | Outbound Message x Status Registers (OMxSR)                                   |

| 16.6.61 | Outbound Message x Descriptor Queue Dequeue Pointer Address Registers         |

|         | (DMxDQDPAR)                                                                   |

| 16.6.62 | Outbound Message x Source Address Registers (OMxSAR) 16-199                   |

|         | - · · · · · · · · · · · · · · · · · · ·                                       |

Freescale Semiconductor xxi

|  |  | ents |

|--|--|------|

| 16.6.63 | Outbound Message x Destination Port Register (OMxDPR) 16-200             |

|---------|--------------------------------------------------------------------------|

| 16.6.64 | Outbound Message x Destination Attributes Register (OMxDATR) 16-201      |

| 16.6.65 | Outbound Message x Double-Word Count Register (DMxDCR) 16-202            |

| 16.6.66 | Outbound Message x Descriptor Queue Enqueue Pointer Address Registers    |

|         | (OMxDQEPAR)                                                              |

| 16.6.67 | Outbound Message x Retry Error Threshold Configuration Register          |

|         | (OMxRETCR)                                                               |

| 16.6.68 | Outbound Message x Multicast Group Registers (OMxMGR) 16-205             |

| 16.6.69 | Outbound Message x Multicast List Registers (OMxMLR) 16-206              |

| 16.6.70 | Inbound Message x Mode Registers (IMxMR)                                 |

| 16.6.71 | Inbound Message x Status Registers (IMxSR)                               |

| 16.6.72 | Inbound Message x Frame Queue Dequeue Pointer Address Registers          |

|         | (IMxFQDPAR)                                                              |

| 16.6.73 | Inbound Message x Frame Queue Enqueue Pointer Address Registers          |

|         | (IMxFQEPAR)                                                              |

| 16.6.74 | Inbound Message x Maximum Interrupt Report Interval Registers            |

|         | (IMxMIRIR)                                                               |

| 16.6.75 | Outbound Doorbell Mode Register (ODMR)                                   |

| 16.6.76 | Outbound Doorbell Status Register (ODSR)                                 |

| 16.6.77 | Outbound Doorbell Destination Port Register (ODDPR) 16-216               |

| 16.6.78 | Outbound Doorbell Destination Attributes Register (ODDATR) 16-217        |

| 16.6.79 | Outbound Doorbell Retry Error Threshold Configuration Register           |

|         | (ODRETCR)                                                                |

| 16.6.80 | Inbound Doorbell Mode Registers (IDMR)                                   |

| 16.6.81 | Inbound Doorbell Status Register (IDSR)                                  |

| 16.6.82 | Inbound Doorbell Queue Dequeue Pointer Address Register (IDQDPAR) 16-222 |

| 16.6.83 | Inbound Doorbell Queue Enqueue Pointer Address Registers                 |

|         | (IDQEPAR)                                                                |

| 16.6.84 | Inbound Doorbell Maximum Interrupt Report Interval Register              |

|         | (IDMIRIR)                                                                |

| 16.6.85 | Inbound Port-Write Mode Register (IPWMR)                                 |

| 16.6.86 | Inbound Port-Write Status Register (IPWSR)                               |

| 16.6.87 | Inbound Port-Write Queue Base Address Register (IPWQBAR) 16-227          |

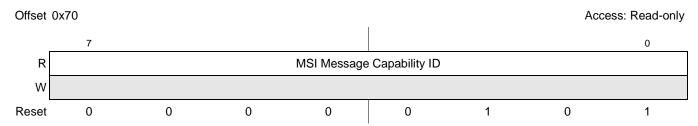

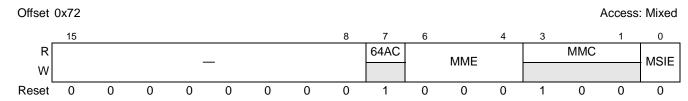

| 17      | PCI Express Controller                                                   |

| 17.1    | Overview                                                                 |

| 17.1.1  | Outbound Transactions                                                    |

| 17.1.2  | Inbound Transactions                                                     |

| 17.2    | Features                                                                 |

| 17.3    | Functional Description                                                   |

| 17.3.1  | Modes of Operation                                                       |

xxii Freescale Semiconductor

| 17.3.2     | PCI Express Transactions                                           |

|------------|--------------------------------------------------------------------|

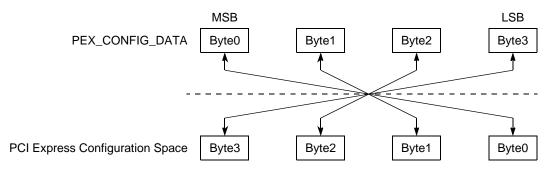

| 17.3.2.1   | Byte Ordering                                                      |

| 17.3.2.2   | Byte Order for Configuration Transactions 17-9                     |

| 17.3.2.3   | Transaction Ordering Rules                                         |

| 17.3.2.4   | Memory Space Addressing                                            |

| 17.3.2.5   | I/O Space Addressing                                               |

| 17.3.2.6   | Configuration Space Addressing                                     |

| 17.3.2.7   | Serialization of Configuration and I/O Writes                      |

| 17.3.3     | Messages                                                           |

| 17.3.3.1   | Outbound ATMU Message Generation                                   |

| 17.3.3.2   | Inbound Messages                                                   |

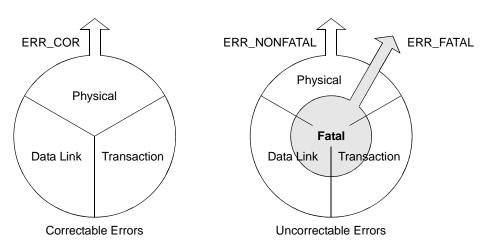

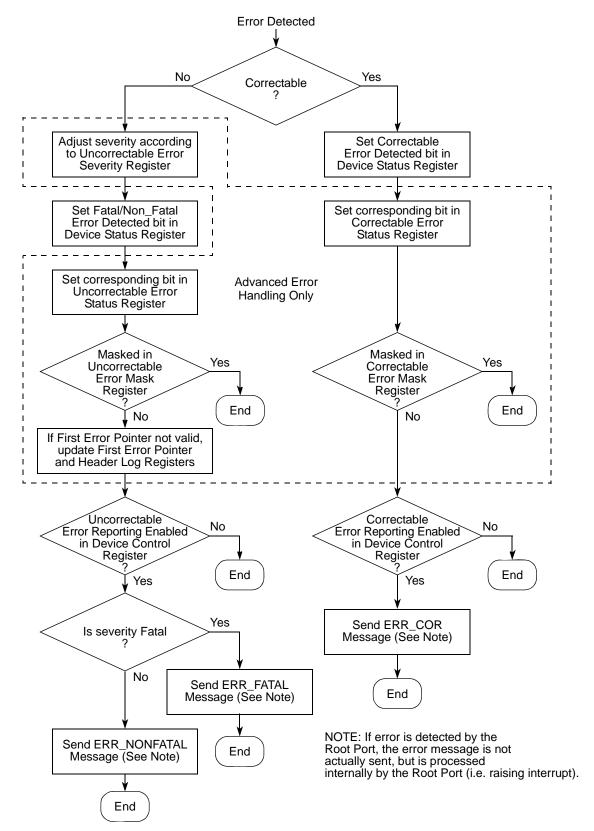

| 17.3.4     | Error Handling                                                     |

| 17.3.4.1   | PCI Express Error Logging and Signaling                            |

| 17.3.4.2   | PCI Express Controller Internal Interrupt Sources                  |

| 17.3.4.3   | Error Conditions                                                   |

| 17.3.5     | Interrupts                                                         |

| 17.3.6     | Initial Credit Advertisement                                       |

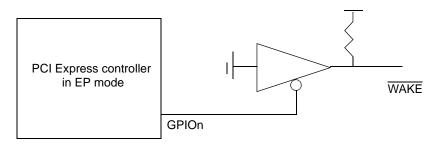

| 17.3.7     | Power Management                                                   |

| 17.3.8     | L2/L3 Ready Link State                                             |

| 17.3.9     | Hot Reset                                                          |

| 17.3.10    | Link Down                                                          |

| 17.3.11    | Initialization/Application Information                             |

| 17.4       | Programming Model                                                  |

| 17.4.1     | PCI Express Memory Mapped Registers                                |

| 17.4.1.1   | PCI Express Configuration Access Registers                         |

| 17.4.1.1.1 | PCI Express Configuration Address Register (PEX_CONFIG_ADDR) 17-27 |

| 17.4.1.1.2 | PCI Express Configuration Data Register (PEX_CONFIG_DATA) 17-28    |

| 17.4.1.1.3 | PCI Express Outbound Completion Timeout Register                   |

|            | (PEX_OTB_CPL_TOR)17-29                                             |

| 17.4.1.1.4 | PCI Express Configuration Retry Timeout Register                   |

|            | (PEX_CONF_RTY_TOR)                                                 |

| 17.4.1.1.5 | PCI Express Configuration Register (PEX_CONFIG) 17-30              |

| 17.4.1.2   | PCI Express Power Management Event and Message Registers 17-31     |

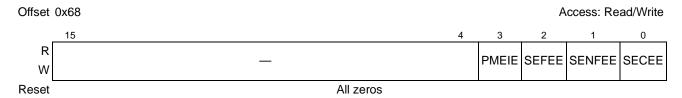

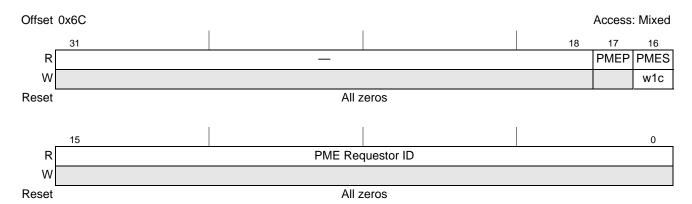

| 17.4.1.2.1 | PCI Express PME and Message Detect Register (PEX_PME_MES_DR) 17-31 |

| 17.4.1.2.2 | PCI Express PME and Message Disable Register                       |

|            | (PEX_PME_MES_DISR)17-33                                            |

| 17.4.1.2.3 | PCI Express PME and Message Interrupt Enable Register              |