Click here for production status of specific part numbers.

DS28C36

### **DeepCover Secure Authenticator**

EVALUATION KIT AVAILABLE

#### **General Description**

The DS28C36 is a DeepCover<sup>®</sup> secure authenticator that provides a core set of cryptographic tools derived from integrated asymmetric (ECC-P256) and symmetric (SHA-256) security functions. In addition to the security services provided by the hardware implemented crypto engines, the device integrates a FIPS/NIST true random number generator (RNG), 8Kb of secured EEPROM, a decrement-only counter, two pins of configurable GPIO, and a unique 64-bit ROM identification number (ROM ID).

The ECC public/private key capabilities operate from the NIST defined P-256 curve and include FIPS 186 compliant ECDSA signature generation and verification to support a bidirectional asymmetric key authentication model. The SHA-256 secret-key capabilities are compliant with FIPS 180 and are flexibly used either in conjunction with ECDSA operations or independently for multiple HMAC functions.

Two GPIO pins can be independently operated under command control and include configurability supporting authenticated and nonauthenticated operation including an ECDSA-based crypto-robust mode to support secureboot of a host processor.

DeepCover embedded security solutions cloak sensitive data under multiple layers of advanced security to provide the most secure key storage possible. To protect against device-level security attacks, invasive and noninvasive countermeasures are implemented including active die shield, encrypted storage of keys, and algorithmic methods.

### **Applications**

- IoT Node Crypto-Protection

- Accessory and Peripheral Secure Authentication

- Secure Storage of Cryptographic Keys for a Host Controller

- Secure Boot or Download of Firmware and/or System

Parameters

DeepCover is a registered trademark of Maxim Integrated Products, Inc.

#### **Benefits and Features**

- ECC-256 Compute Engine

- FIPS 186 ECDSA P256 Signature and Verification

- ECDH Key Exchange with Authentication Prevents Man-in-the-Middle Attacks

- ECDSA Authenticated R/W of Configurable Memory

- FIPS 180 SHA-256 Compute Engine

- HMAC

- SHA-256 OTP (One-Time Pad) Encrypted R/W of Configurable Memory Through ECDH Established Key

- Two GPIO Pins with Optional Authentication Control

Open-Drain, 4mA/0.4V

- Optional SHA-256 or ECDSA Authenticated On/Off and State Read

- Optional ECDSA Certificate to Set On/Off after Multiblock Hash for Secure Boot

- RNG with NIST SP 800-90B Compliant Entropy Source with Function to Read Out

- Optional Chip Generated Pr/Pu Key Pairs for ECC Operations

- 17-Bit One-Time Settable, Nonvolatile Decrement-Only Counter with Authenticated Read

- 8Kbits of EEPROM for User Data, Keys, and Certificates

- Unique and Unalterable Factory Programmed 64-Bit Identification Number (ROM ID)

Optional Input Data Component to Crypto and Key Operations

- I<sup>2</sup>C Communication Up to 1MHz

- Operating Range: 2.2V to 3.63V, -40°C to +85°C

- 6-Pin TDFN Package

Ordering Information appears at end of data sheet.

Typical Application Circuit appears at end of data sheet.

### DS28C36

### DeepCover Secure Authenticator

#### **Absolute Maximum Ratings**

| Voltage Range on Any Pin Relative to GND | 0.5V to 4.0V  |

|------------------------------------------|---------------|

| Maximum Current into Any Pin             | 20mA          |

| Operating Temperature Range              | 40°C to +85°C |

| Junction Temperature                     | +125°C        |

|                                          |               |

| Storage Temperature Range         | -55°C to +125°C |

|-----------------------------------|-----------------|

| Lead temperature (soldering, 10s) | +300°C          |

| Soldering Temperature (reflow)    | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 6 TDFN-EP

| Package Code                            | X14400F+1      |

|-----------------------------------------|----------------|

| Outline Number                          | <u>21-0137</u> |

| Land Pattern Number                     | <u>90-0058</u> |

| Thermal Resistance, Single-Layer Board: | ,              |

| Junction to Ambient ( $\theta_{JA}$ )   | 55°C/W         |

| Junction to Case $(\theta_{JC})$        | 9°C/W          |

| Thermal Resistance, Four-Layer Board:   |                |

| Junction to Ambient ( $\theta_{JA}$ )   | 42°C/W         |

| Junction to Case $(\theta_{JC})$        | 9°C/W          |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

#### **Electrical Characteristics**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.) \text{ (Note 1)}$

| PARAMETER                                      | SYMBOL           | CONDITIONS | MIN                      | TYP | MAX                      | UNITS |

|------------------------------------------------|------------------|------------|--------------------------|-----|--------------------------|-------|

| Supply Voltage                                 | V <sub>CC</sub>  | DS28C36    | 2.97                     | 3.3 | 3.63                     | V     |

| Supply Voltage                                 |                  | DS28C36B   | 2.2                      |     |                          |       |

| Active Supply Current                          | Icc              | (Note 2)   |                          |     | 300                      | μA    |

| Standby Supply Current                         | Iccs             |            |                          |     | 250                      | μA    |

| Computation Current                            | ICMP             | (Note 3)   |                          |     | 7.5                      | mA    |

| GPIO                                           |                  | ·          | · · ·                    |     |                          |       |

| Output Low                                     | PIOVOL           |            |                          |     | 0.4                      | V     |

| Input Low                                      | PIOVIL           |            | -0.3                     |     | V <sub>CC</sub> x<br>0.3 | V     |

| Input High                                     | PIOVIH           |            | V <sub>CC</sub> x<br>0.7 |     | V <sub>CC</sub> + 0.3    | V     |

| Lookogo ourrent                                | ΙL               | DS28C36    | -10                      |     | +10                      | μA    |

| Leakage current                                |                  | DS28C36B   | -1                       |     | +1                       |       |

| ECC ENGINE                                     |                  |            |                          |     |                          |       |

| Generate ECDSA Signature Time                  | t <sub>GES</sub> |            |                          |     | 50                       | ms    |

| Generate ECC Key Pair                          | t <sub>GKP</sub> |            |                          |     | 100                      | ms    |

| Verify ECDSA Signature or Compute<br>ECDH Time | t <sub>VES</sub> |            |                          |     | 150                      | ms    |

| SHA-256 ENGINE                                 |                  | ·          |                          |     |                          |       |

| Computation Time (HMAC or RNG)                 | t <sub>CMP</sub> |            |                          |     | 3                        | ms    |

### DS28C36

## DeepCover Secure Authenticator

### **Electrical Characteristics (continued)**

(T<sub>A</sub> = -40°C to +85°C.) (Note 1)

| PARAMETER                                                                                      | SYMBOL              | CONDITIONS                     |                     | MIN                      | TYP                       | MAX                      | UNITS |

|------------------------------------------------------------------------------------------------|---------------------|--------------------------------|---------------------|--------------------------|---------------------------|--------------------------|-------|

| EEPROM                                                                                         |                     |                                |                     |                          |                           |                          |       |

| W/E Endurance                                                                                  | NCY                 | (Note 4)                       |                     | 100K                     |                           |                          | _     |

| Read Memory Time                                                                               | t <sub>RM</sub>     |                                |                     |                          |                           | 1                        | ms    |

| Write Memory Time                                                                              | t <sub>WM</sub>     |                                |                     |                          |                           | 15                       | ms    |

| Data Retention                                                                                 | t <sub>DR</sub>     | T <sub>A</sub> = +85°C (Note 5 | 5)                  | 10                       |                           |                          | years |

| I <sup>2</sup> C SCL AND SDA PINS (Note 6)                                                     | BR                  |                                |                     | <u> </u>                 |                           |                          |       |

| Low-Level Input Voltage                                                                        | V <sub>IL</sub>     |                                |                     | -0.3                     |                           | 0.3 ×<br>V <sub>CC</sub> | V     |

| High-Level Input Voltage                                                                       | V <sub>IH</sub>     |                                |                     | 0.7 ×<br>V <sub>CC</sub> |                           | V <sub>CC</sub> +<br>0.3 | V     |

| Hysteresis of Schmitt Trigger Inputs                                                           | V <sub>HYS</sub>    | (Note 7)                       |                     |                          | 0.05 ×<br>V <sub>CC</sub> |                          | V     |

| Low-Level Output Voltage at 4mA Sink<br>Current                                                | V <sub>OL</sub>     |                                |                     |                          |                           | 0.4                      | V     |

| Output Fall Time from $V_{IH(MIN)}$ to $V_{IL(MAX)}$ with a Bus Capacitance from 10pF to 400pF | tOF                 | (Note 7)                       |                     |                          | 30                        |                          | ns    |

| Pulse Width of Spikes that are<br>Suppressed by the Input Filter                               | t <sub>SP</sub>     | (Note 7)                       |                     |                          |                           | 50                       | ns    |

| Input Current with an Input Voltage<br>Between 0.1VCCmax and 0.9VCCmax                         | II                  | DS28C36<br>DS28C36B (Note 8    | )                   | -10<br>-1                |                           | +10<br>+1                | μA    |

| Input Capacitance                                                                              | CI                  | (Note 7)                       |                     |                          | 10                        |                          | pF    |

| SCL Clock Frequency                                                                            | f <sub>SCL</sub>    | (Note 9)                       | DS28C36<br>DS28C36B | 0                        |                           | 0.4<br>1                 | MHz   |

| Hold Time (Repeated) START Condition                                                           | <sup>t</sup> HD:STA |                                | DS28C36<br>DS28C36B | 0.6<br>0.45              |                           |                          | μs    |

| Low Period of the SCL Clock                                                                    | tLOW                | (Note 10)                      | DS28C36<br>DS28C36B | 1.3<br>0.65              |                           |                          | μs    |

| High Period of the SCL Clock                                                                   | t <sub>HIGH</sub>   |                                | DS28C36<br>DS28C36B | 0.6                      |                           |                          | μs    |

| Setup Time for a Repeated START<br>Condition                                                   | <sup>t</sup> SU:STA |                                | DS28C36<br>DS28C36B | 0.6<br>0.35              |                           |                          | μs    |

| Data Hold Time                                                                                 | t <sub>HD:DAT</sub> | (Notes 7, 10, 11)              | DS28C36<br>DS28C36B |                          |                           | 0.9<br>0.35              | μs    |

| Data Setup Time                                                                                | t <sub>SU:DAT</sub> | (Notes 10, 12)                 |                     | 100                      |                           |                          | ns    |

| Setup Time for STOP Condition                                                                  | tsu:sto             |                                | DS28C36<br>DS28C36B | 0.6<br>0.35              |                           |                          | μs    |

| Bus Free Time Between a STOP and START Condition                                               | t <sub>BUF</sub>    |                                | DS28C36<br>DS28C36B | 1.3<br>0.6               |                           |                          | μs    |

| Capacitive Load for Each Bus Line                                                              | CB                  | (Notes 9, 13)                  |                     |                          |                           | 400                      | pF    |

| Warm-Up Time                                                                                   | toscwup             | (Note 14)                      | DS28C36<br>DS28C36B |                          |                           | 0.25                     | ms    |

### DS28C36

### DeepCover Secure Authenticator

### **Electrical Characteristics (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$  (Note 1)

- **Note 1:** Limits are 100% production tested at  $T_A = +25^{\circ}C$  and/or  $T_A = +85^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values at +25°C.

- Note 2: Operating current continuously reading memory at 400kHz with < 25ns rise and fall times on SDA and SCL.

- Note 3: Average current drawn from V<sub>CC</sub> during EEPROM read, EEPROM write, RNG calculation, SHA-256 calculation, or ECDSA calculation.

- **Note 4:** Write-cycle endurance is tested in compliance with JESD47H.

- Note 5: Data retention is rested in compliance with JESD47H.

- Note 6: All I<sup>2</sup>C timing values are referred to  $V_{IH(MIN)}$  and  $V_{IL(MAX)}$  levels.

- Note 7: Guaranteed by design and/or characterization only. Not production tested.

- Note 8: I/O pins of the DS28C36B do not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- Note 9: System requirement.

- **Note 10:** t<sub>LOW</sub> min = t<sub>HD:DAT</sub> max + t<sub>EDGE</sub> max + t<sub>SU:DAT</sub> min, where t<sub>EDGE</sub> is rise or fall time. For the DS28C36, t<sub>EDGE</sub> max = 300ns; for the DS28C36B, t<sub>EDGE</sub> max = 200ns. Values greater than these can be accommodated by extending t<sub>LOW</sub> accordingly.

- Note 11: The DS28C36 provides a hold time of at least 100ns for the SDA signal (referred to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL. The master can provide a hold time of 0ns when writing to the device.

- Note 12: The DS28C36 can be used in a standard-mode I<sup>2</sup>C bus system, but the requirement t<sub>SU:DAT</sub> ≥ 250ns must then be met (I<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

- **Note 13:** C<sub>B</sub> = total capacitance of one bus line in pF. The maximum bus capacitance allowable can vary from this value depending on the actual operating voltage and frequency of the application (I<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

- Note 14: I<sup>2</sup>C communication should not take place for max t<sub>OSCWUP</sub> time following a power-on reset.

## DS28C36

## DeepCover Secure Authenticator

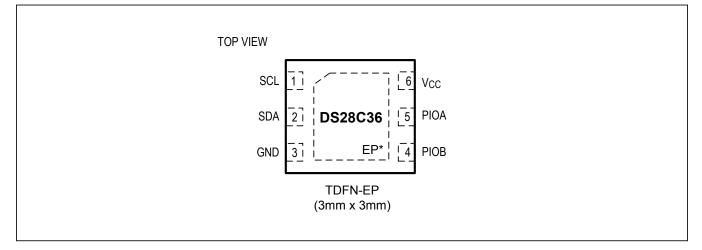

### **Pin Configuration**

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                           |  |  |  |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | SCL             | I <sup>2</sup> C CLK. Connect to $V_{CC}$ with a pullup resistor.                                                                                                                  |  |  |  |

| 2   | SDA             | I <sup>2</sup> C Data. Connect to V <sub>CC</sub> with a pullup resistor.                                                                                                          |  |  |  |

| 3   | GND             | Ground                                                                                                                                                                             |  |  |  |

| 4   | PIOB            | General-Purpose IO                                                                                                                                                                 |  |  |  |

| 5   | PIOA            | General-Purpose IO                                                                                                                                                                 |  |  |  |

| 6   | V <sub>CC</sub> | Supply Voltage                                                                                                                                                                     |  |  |  |

| _   | EP              | Exposed Pad. Solder evenly to the board's ground plane for proper operation. Refer to Application Note 3273: Exposed Pads: <i>A Brief Introduction</i> for additional information. |  |  |  |

### DS28C36

### DeepCover Secure Authenticator

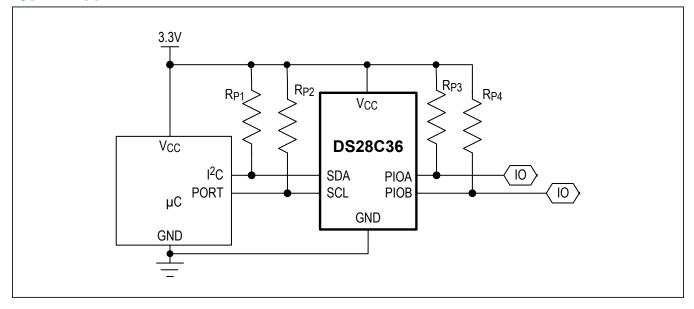

### **Typical Application Circuit**

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE              |

|-------------|----------------|--------------------------|

| DS28C36Q+T† | -40°C to +85°C | 6 TDFN-EP*<br>(2.5k pcs) |

| DS28C36BQ+T | -40°C to +85°C | 6 TDFN-EP*<br>(2.5k pcs) |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T= Tape and reel.

\*EP = Exposed pad.

*†Not recommended for new designs.*

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.