DomBlogSzczegółowy przewodnik po pełnym sumowaniu

Szczegółowy przewodnik po pełnym sumowaniu

W dziedzinie cyfrowej elektroniki i inżynierii komputerowej Adders reprezentują jeden z najważniejszych elementów składowych, kluczowych w budowie i funkcjonalności bardziej skomplikowanych obwodów arytmetycznych.Jako integralne komponenty arytmetycznej jednostki logicznej (ALU), adders ułatwiają liczne operacje obliczeniowe, od podstawowej arytmetyki po złożone logiczne zadania niezbędne do operacji systemowych.Ich konstrukcja, która może się różnić od prostych pół-doradców do bardziej złożonych pełnych dodatków, odgrywa kluczową rolę w zwiększaniu wydajności i szybkości przetwarzania w systemach cyfrowych.Ten artykuł zagłębia się w szczegółową architekturę i funkcjonalne niuanse różnych rodzajów dodatków, ilustrując ich kluczową rolę we współczesnej technologii obliczeniowej i badając ich logikę operacyjną, obwody i aplikacje w szerszym kontekście cyfrowego projektowania logiki.

Katalog

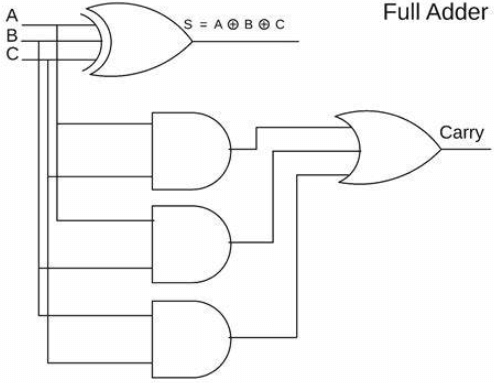

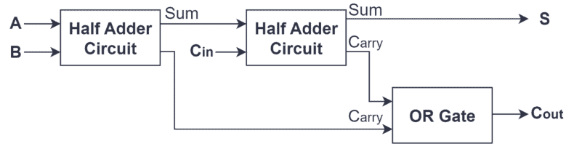

Rysunek 1: Pełny sumator

Adder jest fundamentalnym elementem projektowania inżynierii elektronicznej i cyfrowej logiki i odgrywa centralną rolę w bardziej złożonych systemach komputerowych.W ramach arytmetycznej jednostki logicznej (ALU) sumder obsługuje różne niezbędne zadania komputerowe.Na wydajność i wydajność całego procesora wpływa bezpośrednio projekt i funkcjonalność sumera.

W procesorze sumator jest używany nie tylko do podstawowych operacji arytmetycznych, takich jak dodawanie i odejmowanie, ale także w szerszym zakresie operacji logicznych.Na przykład podczas uruchamiania programów procesor często musi obliczyć nowe adresy pamięci.Zazwyczaj odbywa się to poprzez dodanie lub odejmowanie od bieżącego adresu - zadania podejmowanego przez sumera.Kontrolują liczbę iteracji pętli i ogólny przepływ, zwiększając i zmniejszając liczniki.W bardziej złożonych aplikacjach, takich jak indeksowanie tabeli, adders szybko lokalizują dane, obliczając przesunięcia.Jest to ważne dla systemów zarządzania bazami danych, konstrukcji kompilatora i przetwarzania danych na dużą skalę.Dodatki są również kluczowe we wdrażaniu niektórych technik mapowania w wielopoziomowych systemach pamięci podręcznej, wykorzystując operacje arytmetyczne w celu ustalenia pozycji danych w pamięci podręcznej, w ten sposób optymalizując wydajność dostępu.

Technologicznie dodatki są wdrażane za pomocą różnych projektów obwodów, w tym dodatków równoległych, szeregowych i rurociągów.Równoległe dodatki są preferowane ze względu na ich zdolność do obsługi wielu cyfr jednocześnie, dzięki czemu są odpowiednie do scenariuszy wymagających szybkiego obliczenia.Z drugiej strony dodatki szeregowe przetwarzają jeden bit na cykl zegara i są idealne do środowisk ograniczonych do zasobów lub niskiej mocy.Dodatki rurociągów dzielą proces dodawania na kilka etapów, z których każdy obsługuje część operacji dodawania.Ten projekt znacznie zwiększa szybkość obliczeń, szczególnie w środowiskach obliczeniowych o wysokiej wydajności.

Obwód na pół wadliwa jest fundamentalnym elementem konstrukcyjnym w cyfrowej elektronice, specjalnie zaprojektowanej w celu dodania dwóch pojedynczych cyfr binarnych.Ten obwód stanowi podstawę pełnego sumera i jest kluczem do zrozumienia bardziej złożonych projektów obwodów logicznych.W pół sumera istnieją dwa podstawowe wejścia, oznaczone A i B, które reprezentują odpowiednio Augend i dodatek.Ta konfiguracja umożliwia obliczenie sumy i przeniesienia wyjściowego bez potrzeby wejścia do przenoszenia z poprzednich obliczeń.

Rdzeń pół-adwokata składa się z dwóch bram logicznych: bramy Xor i An i Gate.Brama XOR jest odpowiedzialna za generowanie wyjścia suma.Działa zgodnie z prostą regułą, w której wyświetla 1, jeśli tylko jeden z jego wejść to 1;W przeciwnym razie wyświetla 0. Brama i, z drugiej strony, obsługuje wyjście noszenia.Produkuje 1 tylko wtedy, gdy oba jego dane wejściowe są 1, idealnie dostosowując się do podstawowych wymagań dodawania binarnego.

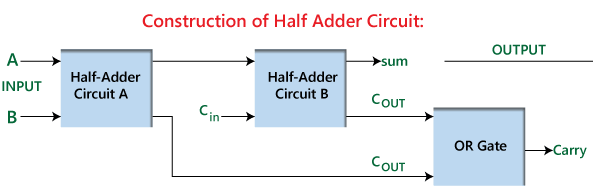

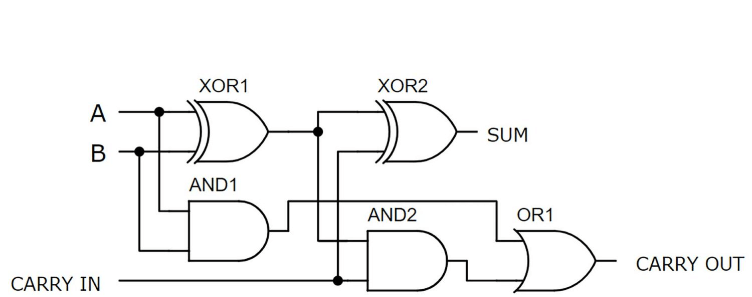

Rysunek 2: Konstrukcja połowy sumera

Ta wydajna i prosta konstrukcja pozwala półprodukcyjnym sumę nie tylko wykonanie podstawowego dodatku binarnego niezależnie, ale także służyć jako element konstrukcyjny do tworzenia pełnego sumera.Pełny sumator jest konstruowany przez połączenie dwóch połowy dodatków z dodatkową lub bramą.W tej konfiguracji pierwsza połowa sumator przyjmuje początkowe zadanie dodawania, generując wstępną sumę i noszenie.Następnie sumator drugiej połowy przetwarza przenoszenie od pierwszego wraz z dodatkowym wejściem do przeniesienia.Wreszcie, brama lub łączy dwa wyjścia przenoszenia, aby wytworzyć ostateczną moc przenoszenia.Układ ten poprawia funkcjonalność sumera, umożliwiając mu obsługę bardziej złożonych wielobitowych zadań dodawania, pokazując powszechne zastosowanie i znaczenie pół dodawania w projektowaniu obwodów cyfrowych.

Pełny sumator jest zaawansowanym komponentem cyfrowego projektowania logiki, wyposażonego do obsługi dodania trzech pojedynczych wejść binarnych, powszechnie oznaczonych jako A, B i CIN (CIN).Ta konstrukcja umożliwia pełnego sumera wydajne przetwarzanie złożonych dodatków binarnych poprzez włączenie przenoszenia z poprzednich obliczeń niższego rzędu do jednej operacji.

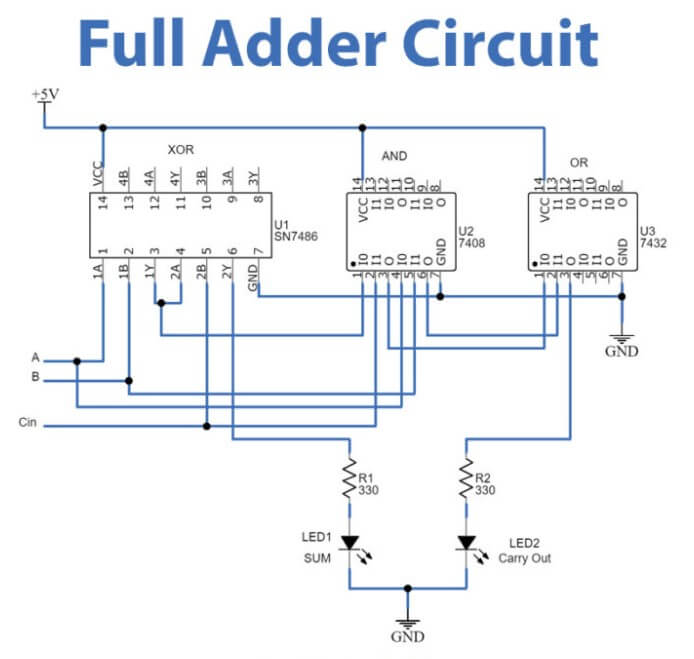

Rysunek 3: Pełny obwód sumera

Funkcjonalnie pełny sumator może wysyłać dwucyfrową sumę, co oznacza, że jego wyjście może wynosić od 0 do 3, a także może wytworzyć przeniesienie (cout).Dzieje się tak, ponieważ gdy wszystkie bity wejściowe są ustawione na 1 (a = 1, b = 1, cin = 1), suma wyjściowa będzie 1 (reprezentująca binarne 01) i generowane jest przeprowadzenie 1, co wskazuje, że wskazuje, że wskazuje na toDodatkowe noszenie należy przekazać do następnego wyższego bitu.

Strukturalnie pełny sumator ogólnie składa się z dwóch połowy addyterów i jednego lub bramy.Ładca pierwszej połowy przyjmuje dane wejściowe A i B, generując początkową sumę i sygnał przenoszenia.Ta początkowa suma jest następnie podawana wraz z przeniesieniem (CIN), do drugiego pół-addera.Rolą drugiej połowy Addera jest dodanie tej suma z pierwszej połowy sumera do CIN, wytwarzając kolejną sumę i nową moc przenoszenia.Jednocześnie wyjście przenoszenia z pierwszej połowy sumera i wyjście przenoszenia z drugiej połowy sumowania są scalone przez bramę OR, kulminacją końcowego przeniesienia (cout) pełnego sumera.Projekt tej struktury zapewnia, że pełny sumnik skutecznie obsługuje propagację przewoźników, co czyni ją idealną do wykonywania wielobitowych dodatków binarnych.Zatem projekt pełnego sumera nie tylko przyspiesza przetwarzanie danych i zwiększa wydajność, ale także upraszcza złożoność implementacji sprzętowej poprzez prostą kombinację bram logicznych, co czyni go niezbędnym komponentem w zakresie dodawania wielokierunkowego i arytmetycznej jednostki logicznej (ALU).

|

Parametry

|

Half Adder

|

Pełny sumator

|

|

Opis

|

Half Adder to kombinacyjna logika

Obwód, który dodaje dwie 1-bitowe cyfry.Pół-addder wytwarza sumę tych dwóch

Wejścia.

|

Pełny sumator to logika kombinacyjna

Obwód, który wykonuje operację dodawania na trzech jednolitowych liczb binarnych.

Pełny sumer wytwarza sumę trzech danych wejściowych i wartość przenoszenia.

|

|

Poprzedni noszenie

|

Poprzednie noszenie nie jest używane.

|

Zastosowana jest poprzednia noszenie.

|

|

Wejścia

|

W połowie sumera istnieją dwa bity wejściowe (a,

B).

|

W pełnym sumowaniu istnieją trzy bity wejściowe

(A, B, CW).

|

|

Wyjścia

|

Wygenerowane wyjście ma dwa bity sumowe

i przenieś z wejścia 2 bitów.

|

Wygenerowane wyjście ma dwa bity sumowe

i przenieś z wejścia 3 bitów.

|

|

Użyty jako

|

Nie można użyć obwodu półocesyjnego

w taki sam sposób jak obwód pełny.

|

Pełny obwód sumowania można zastosować na miejscu

połowy obwodu sumera.

|

|

Funkcja

|

Jest prosty i łatwy do wdrożenia

|

Projekt pełnego sumera nie jest taki

Prosty jak połowa sumera.

|

|

Logiczne wyrażenie

|

Logiczne wyrażenie dla połowy sumera to:

S = a⊕b;C = a*b.

|

Logiczne wyrażenie dla pełnego sumera to:

S = a⊕b⊕cin;Cna zewnątrz= (a*b)+(cW*(a⊕b)).

|

|

Bramki logiczne

|

Składa się z jednej ex-lub bramki i jednej i

brama.

|

Składa się z dwóch ex-or, dwóch i bram,

i jedna lub brama.

|

|

Aplikacje

|

Jest używany w kalkulatorach, komputerach,

cyfrowe urządzenia pomiarowe itp.

|

Jest używany w wielu bitach,

Cyfrowe procesory itp.

|

|

Alternatywna nazwa

|

Nie ma alternatywnej nazwy dla połowy

sumator.

|

Pełny sumator jest również znany jako obrońca tętni

sumator.

|

Wykres

1: Różnica między połową sumera a pełnym sumorem

Tabela prawdy pełnego sumera jest kluczem do zrozumienia jego logiki operacyjnej, szczegółowo opisującą dokładną zależność między kombinacjami wejściowymi binarnymi a odpowiednimi wynikami.Ta tabela pokazuje wszystkie potencjalne scenariusze wejściowe i ich wyniki, co czyni ją niezbędnym narzędziem w projektowaniu i weryfikacji cyfrowych obwodów logicznych.Pełny sumator przetwarza trzy dane wejściowe: A, B i A CIN (CIN), z których każdy może wynosić 0 lub 1. Powoduje to osiem możliwych kombinacji danych wejściowych.

Dla każdej z tych kombinacji wyniki z pełnego sumera obejmują sumę (sumę) i przeniesienie (cout).Suma jest dodawanie modulo-2 (operacja XOR) trzech wejść-A, B i CIN.Przenoszenie występuje, gdy co najmniej dwa bity wejściowe to 1. Odzwierciedla to pełną zdolność sumera do obsługi przeniesienia w operacjach dodatkowych sekwencyjnych, zapewniając dokładność w obliczeniach o wyższych bitach.

Aby zilustrować, rozważ scenariusz wejściowy, w którym wszystkie dane wejściowe to 0 (a = 0, b = 0, c-in = 0).Suma wyjściowa wyniesie 0, a przeniesienie wyniesie również 0, co wskazuje, że nie ma dodatkowej sumy ani przenoszenia do zarządzania.Jeśli tylko jeden bit wejściowy to 1, taki jak A = 1, B = 0, C-in = 0, suma wyjściowa wynosi 1 bez przeniesienia, co pokazuje, że nie ma potrzeby przenoszenia przenoszenia na wyższy bit.Gdy dwa bity wejściowe wynoszą 1, takie jak A = 1, B = 1, C-in = 0, suma wyjściowa wynosi 0 (ponieważ 1+1 równa się 2 w binarnym, a modulo-2 powoduje 0), ale przeniesienie-Wynosi 1, wskazując na przeniesienie, które należy przekazać do następnego wyższego bitu.Najbardziej złożony scenariusz występuje, gdy wszystkie trzy bity wejściowe to 1 (a = 1, b = 1, c-in = 1);Suma wyjściowa wynosi 1, a przeprowadzanie 1, co sugeruje, że zarządzanie noszeniem może być również wymagane przy jeszcze wyższych bitach.

|

A

|

B

|

CW

|

S

|

Cna zewnątrz

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

Wykres 2: Pełny stół prawdy sumera

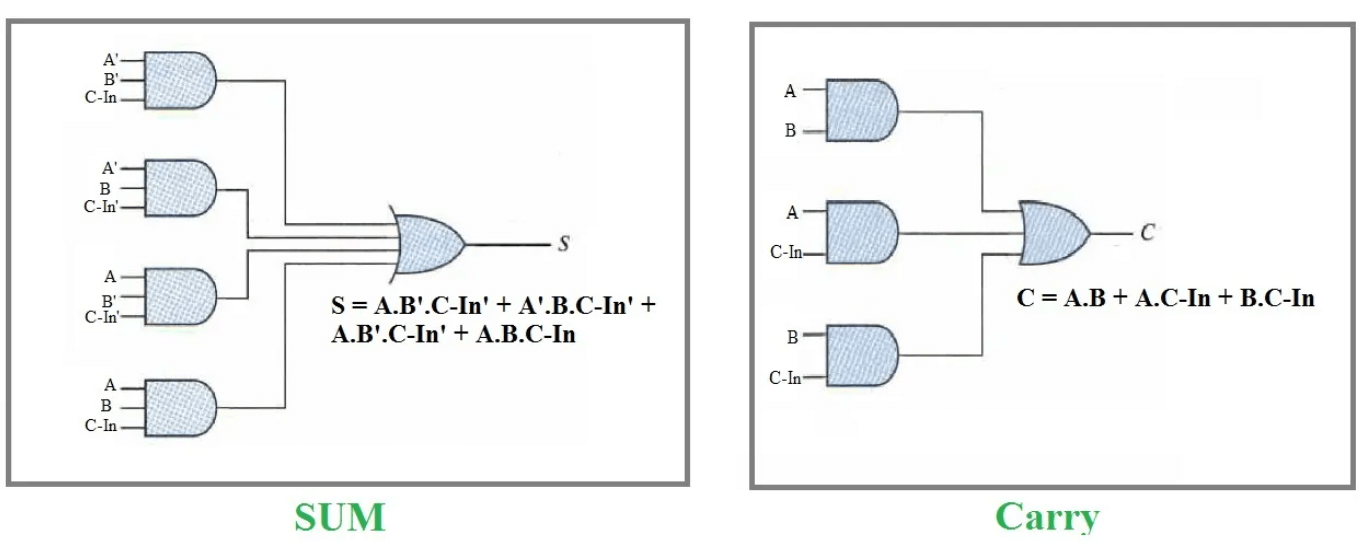

Zrozumienie pełnego sumera polega na analizowaniu jego funkcjonalności za pomocą tabeli prawdy, w której różne kombinacje wartości wejściowych A, B i C-In prowadzą do wyników sumowania i cout.Aby uchwycić operację, upraszczamy równania logiczne krok po kroku.

Wyrażenie logiczne dla sumy

Równanie rozpoczyna się od różnych przypadków, w których suma jest równa 1:

• A „B” Cin + A 'B CIN' + A B 'CIN' + AB CIN

To równanie można skondensować przez grupowanie warunków z CIN i bez CIN:

• CIN (A „B” + AB) + CIN ”(A„ B + A B ”)

To uproszczenie prowadzi do łatwiejszego wdrożenia:

• Cin Xor (a xor b)

Ta reprezentacja pokazuje, że suma wyjściowa jest zasadniczo operacją XOR wśród A, B i CIN, przechwytując rdzeniowe zachowanie dodatku binarnego, w którym przełącza sumę na podstawie nieparzystej liczby.

Logika dla Cout

Zaczynając od warunków, w których generowane jest przeniesienie:

• A 'B CIN + A B' CIN + AB C-IN ' + AB CIN

Upraszczając równanie, identyfikujemy terminy, które zwykle obejmują generowanie przeniesienia:

• AB + B CIN + A CIN

Szukając innej metody wdrożenia Cout, równanie można zreorganizować:

• AB + A CIN + B C-IN (A + A ')

Rozszerza się i rekombinuje, aby uchwycić wszystkie scenariusze, w których co najmniej dwa dane wejściowe to 1:

• AB CIN + AB + A C-in + A 'B Cin

• AB (1 + CIN) + C-in + A 'B Cin

• AB + A C-in (B + B ') + A' B CIN

• AB + A B 'CIN + A' B CIN

• AB + CIN (A „B + A B”)

Ostateczny kompaktowy formularz dla Cout:

• AB + CIN (A XOR B)

Ta wersja równania przeniesienia pokazuje, w jaki sposób Cout jest wytwarzany albo, gdy zarówno A, jak i B wynoszą 1, lub gdy jeden z A lub B jest 1 wraz z przeniesieniem, w ten sposób, obejmując logikę potrzebną do zarządzania propagacją przenoszenia w wieluDodatek binarny.Ta usprawniona logika jest szczególnie przydatna do wdrażania wydajnych obwodów cyfrowych.

Rysunek 4: Równania pełnego sumera

Wdrożenie pełnego obwodu sumera polega na starannym montażu dwóch połowy dodatków i bramki OR, aby utworzyć urządzenie zdolne do skutecznego obsługi dodania trzech pojedynczych wejść binarnych.Ten układ optymalizuje złożoność obwodu i zapewnia zarówno wydajne, jak i dokładne obliczenia.

Na początek pierwsza połowa sumera przyjmuje dwa pierwotne wejścia binarne, A i B, które są głównymi cyframi, które należy dodać.Jego kluczowym zadaniem jest obliczenie sumy i początkowego przeniesienia tych dwóch liczb.Tutaj pierwsza połowa sumera zapewnia dwa wyniki: sumę początkową (sum1) i początkowe przeniesienie (Carry1).SUM1 pochodzi z operacji XOR A i B, co wskazuje, czy suma ma nieparzystą liczbę 1.Noszenie1, wynik i działanie między A i B, wskazuje, czy obie cyfry wynoszą 1, wymagając przeniesienia do następnego wyższego bitu.

Następnie sumer drugiej połowy dołącza do procesu.Używa sumy SUM1 i trzeciego wejścia CIN (przeniesienie z poprzednich obliczeń) jako jego wejścia.Druga połowa sumera wytwarza dwa wyjścia: końcowy wynik (sum2) i wtórne przeniesienie (Carry2).SUM2, który jest wynikiem XOR SUM1 i CIN, reprezentuje końcową sumę trzech wejść, wyświetlając zagregowany dodatek binarny.Carry2, wyłaniający się z i działań między sum1 i CIN, wskazuje na przeniesienie generowane przez te komponenty.

Rysunek 5: Pełny obwód sumera przy użyciu dwóch połowy sumera

Wreszcie, aby ukończyć pełny projekt sumera, brama lub brama jest wymagana do obsługi wyjściowych przeniesienia przenoszenia 1 i przeniesienia 2 z obu połowy dodatków.Ta lub brama zapewnia, że każde przenoszenie wygenerowane podczas obliczeń jest prawidłowo przekazywane do ostatecznego wyjścia.Dlatego końcowa wyjście pełnoprawnego dla przeniesienia (cout) jest lub wynikiem Carry1 i Carry2.Włączenie tej lub bramki gwarantuje, że wszystkie potencjalne przenoszenie jest dokładnie obliczane i przekazywane na wyższy poziom w wielu bitowych operacjach dodawania, zapewniając integralność operacji arytmetycznej na wielu bitach.

Pełne dodatki odgrywają niezbędną rolę w projektowaniu logiki cyfrowej, oferując wiele korzyści, które czynią je niezbędnymi w różnych scenariuszach przetwarzania i przetwarzania danych.Ich podstawowe zalety obejmują niezwykłą elastyczność, szybkie prędkości przetwarzania i wydajne zarządzanie noszeniem.Cechy te sprawiają, że pełne dodatki są idealne do wykonywania złożonych operacji arytmetycznych i funkcji logicznych, szczególnie w aplikacjach wymagających sekwencyjnego dodawania wielu bitów.

Zalety

Elastyczność: Pełne dodatki doskonaleniają ich zdolność do przetwarzania wielu binarnych danych wejściowych (A, B i CIN) jednocześnie.Można je również rozszerzyć na większe tablice sumera, aby obsłużyć dłuższe liczby binarne.Ta skalowalność jest ważna dla budowania wysokowydajnych jednostek logicznych arytmetycznych (ALUS), które muszą przeprowadzić misterne operacje arytmetyczne i logiczne.

Szybkość: Dzięki wewnętrznej architekturze przetwarzania równoległego, pełne dodatki mogą uzupełnić dodanie wszystkich wejść w jednym cyklu zegara, a jednocześnie określać, aby przenieść wyjścia.Ta zdolność obsługuje operacje ciągłego dodawania i jest niezbędne do przetwarzania danych w czasie rzeczywistym w nowoczesnych mikroprocesorach i szybkich urządzeniach komputerowych.

Niedogodności

Jednak pełne dodatki przedstawiają również znaczące wady:

Złożoność w projektowaniu i implementacji: Pełne dodatki obejmują wiele bram logicznych i wielopoziomowe propagacja przenoszenia, co czyni ich projektowanie.Ta złożoność nie tylko zwiększa koszty produkcji, ale może również wpływać na niezawodność obwodów.

Problemy związane z opóźnieniem propagacji: Rozmnażanie przenoszenia może przechodzić przez kilka bram logicznych, z których każda dodaje opóźnienia.Może to ograniczyć ogólną prędkość obliczeniową podczas operacji na dużą skalę, szczególnie w rozległych systemach komputerowych oraz w projektowaniu integracji bardzo dużej skali (VLSI) i szybkich procesorów.Opóźnienie może stać się znaczącym wąskim gardłem w wydajności.

Aby złagodzić te problemy, inżynierowie ciągle badają bardziej wydajne projekty obwodów.Strategie obejmują stosowanie szybszych technologii bram logicznych, optymalizację układów obwodów w celu skrócenia długości ścieżki oraz opracowywanie zaawansowanych technologii, takich jak dodatki do przeniesienia, aby zminimalizować opóźnienia w propagacji przenoszenia.

Pełne dodatki są szeroko wykorzystywane w cyfrowej logice, cenione za ich elastyczność i wydajność, co czyni je kluczowymi dla wielu zadań obliczeniowych i przetwarzania danych.Ich aplikacja obejmuje podstawowe operacje arytmetyczne po złożone przetwarzanie sygnału i kontrolę systemu.Oto szczegółowe spojrzenie na niektóre kluczowe obszary, w których pełne dodatki są integralne.

Obwody arytmetyczne

Jednym z najprostszych zastosowań pełnych dodatków jest obwody arytmetyczne, w których wykonują dodatek binarny.Szczególnie kluczowe w dodawaniu wielu bitów, pełne dodatki zarządzają dłuższymi sekwencjami binarnymi poprzez kaskadowanie.W tym układzie każdy pełny sumator obsługuje dodatek do swojej pozycji bitowej i przeniesienie z dolnego bitu, a następnie przekazuje nową noszenie do pełnego sumera następnego wyższego bitu.Ta kaskada umożliwia kompleksowy wielobitowy dodatek w całym zakresie cyfr.

Przetwarzanie danych

Pełne dodatki odgrywają również kluczową rolę w zaawansowanych zadaniach przetwarzania danych, takich jak cyfrowe przetwarzanie sygnałów (DSP) do filtrowania i transformacji Fouriera, w których potrzebne są precyzyjne i szybkie operacje arytmetyczne.Ponadto, w sferze bezpieczeństwa informacji, w tym szyfrowanie danych i wykrywanie błędów i wykrywania błędów i algorytmów korekcji, takich jak kontrole parytetów i generowanie kodu kontroli redundancji (CRC), pełne dodatki są kluczowe dla wykonywania niezbędnych operacji bitowych.

Liczniki

W licznikach cyfrowych pełne dodatki są niezbędne do wdrażania zarówno funkcji przyrostowych, jak i zmniejszających, szczególnie w licznikach modułowych i synchronicznych.Dokładnie zarządzają nośnymi i pożyczkami, aby zapewnić precyzyjne liczenie.

Multipleksery (MUX) i demultipleksery (Demux)

W multiplekserach i demultiplekserach pełne dodatki odgrywają kluczową rolę w wyborze kanałów i dystrybucji danych.Uczestniczą w logice, która określa, które kanały są używane do wprowadzania danych i wyjścia, podejmując decyzje w oparciu o sygnały kontrolne logiki.

Technologia pamięci

W adresie pamięci pełne dodatki pomagają generować sygnały adresowe do dynamicznego dostępu do lokalizacji pamięci.Jest to szczególnie ważne w dynamicznej pamięci losowej (DRAM) i innych systemach pamięci masowej, w których pełne dodatki obsługują obliczenia złożonych adresów w celu zwiększenia wydajności dostępu do pamięci.

Arytmetyczne jednostki logiczne (ALU)

Wreszcie, jako podstawowe komponenty arytmetycznych jednostek logicznych w mikroprocesorach i cyfrowych procesorach sygnałowych, pełne dodatki są kluczowe.ALU obsługuje wszystkie operacje arytmetyczne i logiczne, a pełne dodatki zapewniają przetwarzanie danych zarówno szybko, jak i dokładnie.

Pełne dodatki można konstruować przy użyciu różnych bram logicznych i konfiguracji.Tutaj badamy cztery różne implementacje, podkreślając ich konfigurację i niuanse operacyjne.

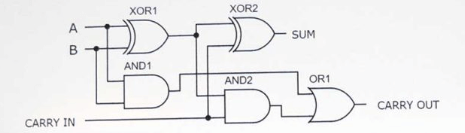

Pełny sumator zbudowany z XOR i lub bramkami

Rysunek 6: Pełny sumator zbudowany z XOR i lub lub bram logiki

Ten przykład prezentuje pełny adder zbudowany na tablicy chleba za pomocą dyskretnych tranzystorów.Konfiguracja obejmuje pięć bram logicznych: dwie bramy Xor, dwa i bramy oraz jedną lub bramę, wymagając łącznie 21 tranzystorów.Wejścia A i B są podłączone do górnej górnej części Breadboard, otrzymując zasilanie +5 V.Te wejścia są kontrolowane za pomocą dwóch przełączników przełączających.Dwie diody LED w lewym górnym rogu wskazują stany wejściowe A i B, a dwie diody LED po prawej stronie wyświetlają wyjścia.Rezystory stosowane w obwodzie to 2,2K omów.Gdy wejścia A i B są włączone, a przeniesienie jest wyłączone, wyjście pokazuje wartość binarną 10, reprezentując sumę 2 (1 + 1 + 0 = 10).Bramy Xor, zbudowane z pierwszymi 12 tranzystorami, obsługują podstawowe podsumowanie, podczas gdy dolna połowa płyty chlebowej zawiera i / / lub bramki do operacji przenoszenia, okablowanie oznaczone kolorami zwiększa przejrzystość i rozwiązywanie problemów.

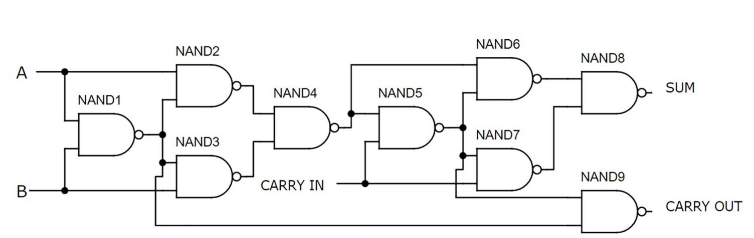

Pełny sumator za pomocą bram NAND

Rysunek 7: Pełny sumator za pomocą bram NAND

Ten pełny sumator wykorzystuje dziewięć bram NAND, z każdą bramą wykonaną z dwóch tranzystorów, łącznie 18 tranzystorów.Ta metoda jest jednym z najprostszych i najbardziej wydajnych sposobów konstruowania pełnego sumera przy użyciu dyskretnych komponentów.Wszystkie bramki są montowane w górnej połowie deski chleba, podczas gdy przełączniki zajmują dolną połowę.Funkcjonalność obwodu wykazano przy wejściach A i B ON, a przeniesienie, co powoduje wyjściową wartość binarną wynoszącą 10, co odpowiada dziesiętnemu 2.

Pełny sumator z ani bramą

Rysunek 8: Pełny sumator z bramą i bramą

Skonstruowany z dziewięcioma ani bramkami, z których każdy wymaga dwóch tranzystorów, ta konfiguracja wykorzystuje również 18 tranzystorów.Budowanie pełnego sumera z bramą i bramami stanowi dobrą alternatywę, ale obejmuje bardziej złożone okablowanie w porównaniu z bramami NAND.Każdy tranzystor w bramie NOR jest uziemiony, z kolekcjonerami podłączonymi pomarańczowymi przewodami zworki, aby zapewnić schludne i zorganizowane okablowanie.Ta konfiguracja jest pokazywana przy użyciu wejściowych A i B aktywowanych i dezaktywowanych przeniesienia, co prowadzi do wyjść, w których przeniesienie jest aktywne, a suma jest wyłączona.

Podczas tej eksploracji technologii sumera, od podstawowych połowy dodatków po wyrafinowane pełne projekty sumderów, jest oczywiste, że te elementy są fundamentalne dla rozwoju cyfrowej elektroniki.Charakterystyka operacyjna i przykłady wdrożenia zapewniły podkreślenie wszechstronności i wydajności dodatków w różnych ustawieniach obliczeniowych.Badając strukturę i funkcję dodatków, szczególnie poprzez ich tabele prawdy i równania charakterystyczne, uzyskujemy cenny wgląd w ich możliwości i ograniczenia.Ta wiedza ma zasadnicze znaczenie w rozwijaniu projektowania bardziej wydajnych i szybszych systemów obliczeniowych.Ostatecznie adders nie tylko upraszczają złożone obliczenia binarne, ale także umożliwiają rozprzestrzenianie się technologii w obszarach tak różnorodnych, jak przetwarzanie danych, alokacja pamięci i cyfrowe przetwarzanie sygnałów.W miarę ewolucji technologii cyfrowej trwające udoskonalenie i innowacje w projektowaniu sumderów będą nadal kamieniem węgielnym w opracowywaniu bardziej zaawansowanych architektur obliczeniowych, zapewniając, że te podstawowe komponenty pozostaną w centrum projektowania i wdrażania systemu cyfrowego.

Często zadawane pytania [FAQ]

1. Co to jest pełny obwód sumera?

Pełny sumator to obwód cyfrowy, który dodaje trzy bity binarne do wytworzenia suma i wyjściu przenoszenia.Został zaprojektowany do obsługi dodania trzech danych wejściowych: dwóch znaczących bitów i jednego bitu przeniesienia z poprzedniego dodatku.Umożliwia to stosowanie go w kolejnych etapach dodawania wielu liczb binarnych.

2. Ile i lub, czy XOR w pełnym sumie?

Typowy pełny sumator zawiera:

Dwie bramy Xor do generowania sumy.

Dwa i bramy przyczyniają się do obliczeń przeprowadzania.

Jeden lub brama, aby sfinalizować wyjście przeniesienia.

3. Co to jest wejście do przenoszenia w pełnym posładzie?

Wejście do przenoszenia (CIN) w pełnym sumowce to bit przenoszenia po dodaniu poprzednich niższych znaczących bitów w wielobitowym dodatku binarnym.Umożliwia pełnego sumera rozważenie tego poprzedniego noszenia przy obliczaniu bieżącej suma i nowego przeniesienia.

4. Po co używać pełnego sumera zamiast połowy sumowania?

Zamiast połowy sumera używana jest pełna sumator, ponieważ może dodać trzy bity (w tym przenoszenie z poprzednich dodatków), dzięki czemu nadaje się do łączenia łączenia, aby dodać liczby wielobitowe.Połowa adwokat może dodać tylko dwa bity i nie ma przepisu dotyczących przeniesienia, co ogranicza jego użycie do najprostszych form dodatku binarnego bez sekwencyjnej propagacji przeniesienia.