Innowacyjny przewodnik po JK Flip-Flops: Analiza tabel prawdy, mechanizmy i zastosowania strategiczne

W tym artykule bada architekturę, działanie i różnorodne zastosowania JK Flip-Flop, zaczynając od podstawowej struktury i relacji wejściowych, poprzez szczegółową mechanikę operacyjną, po strategiczne implementacje w złożonych systemach cyfrowych.Dyskurs rozszerza się na rozróżnienie między wariantami wyzwalanymi krawędziami i poziomem, analizując ich odpowiednie narzędzia w środowiskach synchronicznych i asynchronicznych.Katalog

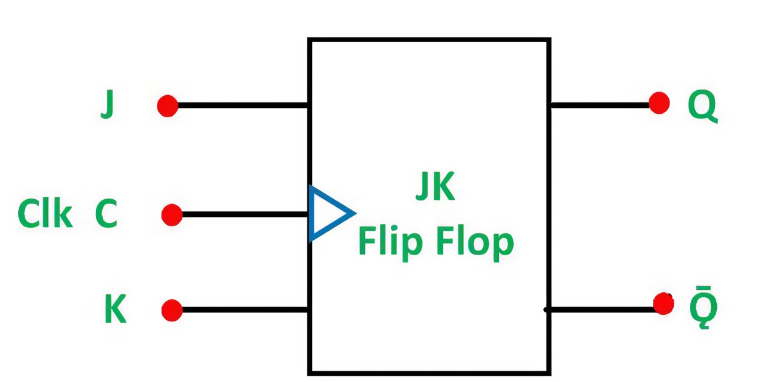

Rysunek 1: Flip-flop JK

Podstawy JK Flip-Flop

JK Flip-Flop to podstawowy element elektroniki cyfrowej, zaprojektowany do przechowywania pojedynczej informacji.Opiera się na prostszym flip-flopie SR, dodając informacje zwrotne, co pomaga zapobiegać błędom znanym jako „warunki wyścigu”, w których moc wyjściowa staje się niestabilna.

Ten Flip-Flop ma dwa główne wejścia, J (Set) i K (Reset) oraz dwa wyjścia: Q i jego uzupełnienie, Q '.Wyjścia te stale odzwierciedlają obecny stan i jego przeciwieństwo, umożliwiając obwodzie dostosowanie i reagowanie na zmiany wejściowe w czasie rzeczywistym.

Flip-Flop JK działa w określony sposób w zależności od wartości wejściowych:

• Gdy zarówno J, jak i K są 0: Flip-Flop utrzymuje swój obecny stan.Nie występują żadne zmiany.

• Gdy zarówno J, jak i K są 1: Flip-Flop przełącza swój stan.Jeśli Q to 0, staje się 1;Jeśli Q to 1, przełącza się na 0. Ta akcja przełączania jest kluczową cechą, która odróżnia Flip-Flop JK od prostszych projektów.

• Gdy J wynosi 1, a K wynosi 0: Flip-Flop ustawia swój stan, czyniąc Q równą 1.

• Gdy J wynosi 0, a K to 1: Flip-Flop resetuje się, czyniąc Q równą 0.

Działanie JK Flip-Flop

Flip-Flop JK odgrywa kluczową rolę w obwodach cyfrowych, zarządzając pamięcią i czasem poprzez skoordynowaną odpowiedź na sygnały wejściowe i impulsy zegara.Jego działanie zależy w dużej mierze od czasu wejść J i K względem sygnału zegara, który określa, jak zmieniają się stany wyjściowe (Q i Q̅).Ta synchronizacja zapewnia, że Flip-Flop zachowuje się przewidywalnie w różnych zastosowaniach obwodów.Flip-flop polega na zarządzaniu tymi zmianami stanu.

Trzymanie obecnego stanu- Gdy zarówno wejścia J, jak i K są niskie (0), Flip-Flop zachowuje swój obecny stan.Bramy logiczne skutecznie „zablokują” wyjścia, zapewniając, że poprzedni stan (wysoki lub niski) jest utrzymywany.Ta funkcja trzymania jest poważna w aplikacjach, w których dane muszą pozostać stabilne, dopóki nie będzie określona zmiana.

Ustawienie wysokiego wyjścia (stan ustawiony) -Gdy występuje impuls zegara, a J jest wysoki (1), podczas gdy K pozostaje niski (0), bramy logiczne dostosowują się do ustawienia Flip-Flop.Doprowadza to wyjście Q do wysokiego stanu (1).Jest to przydatne w sytuacjach, w których obwód musi uruchomić wysokie wyjście, na przykład aktywację urządzenia lub przechowywanie „1” w pamięci.

Wyczyszczenie niskiego wyjścia (stan resetowania) - Jeśli J jest niski (0), a K jest wysoki (1) w momencie impulsu zegara, przerzuca się do stanu resetowania, zmuszając Q do niskiego poziomu (0).To działanie resetowania jest często używane w obwodach, które wymagają stanu domyślnego lub oczyszczonego po zakończeniu operacji, takich jak wyczyszczenie danych z pamięci.

Przełączanie wyjścia - Unikalna funkcja Flip-Flop pojawia się, gdy zarówno J, jak i K są wysokie (1).Po przybyciu impulsu zegara przełącza się, przełączając wyjście ze stanu bieżącego na przeciwny.Jeśli Q jest wysoki, staje się niski, a jeśli Q jest niski, staje się wysoki.Ta funkcja przełączania jest nalegająca w aplikacjach takich jak liczniki lub urządzenia, które muszą automatycznie naprzemiennie między stanami.

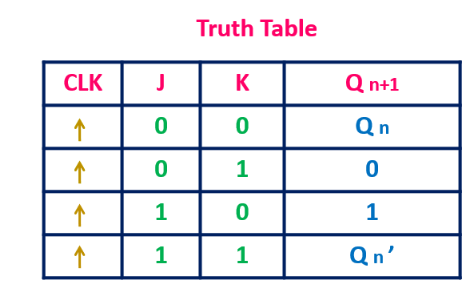

Rysunek 2: Tabela prawdy Flip-Flop JK

Analiza Tabeli Flip-Flop Table Tabela prawdy JK

Tabela prawdy JK Flip-Flop jest kluczowym narzędziem do wizualizacji, w jaki sposób reaguje na różne sygnały wejściowe zsynchronizowane z impulsami zegara.Ta tabela pomaga zarówno projektować, jak i rozwiązywać problemy z obwodami cyfrowymi, pokazując, jak zmieniają się wyjścia Flip-Flop w oparciu o różne warunki wejściowe.

• Zarówno J, jak i k niski (j = 0, k = 0): Gdy oba wejścia wynoszą 0, Flip-Flop utrzymuje swój obecny stan.Niezależnie od tego, czy Q jest wysoki, czy niski, pozostaje niezmieniony.Jest to godne uwagi dla obwodów, w których poszukiwana jest stabilna retencja danych, takich jak elementy w pamięci, w których zachowanie obecnego stanu jest odpowiednie do momentu uruchomienia określonej zmiany.

• j high, k niski (j = 1, k = 0): Gdy J wynosi 1, a K 0, Flip-Flop ustawia wyjście Q na wysoki (1).Ten warunek ustawienia jest przydatny w aplikacjach, które wymagają precyzyjnego spustu do aktywacji operacji, takich jak włączenie urządzenia lub inicjowanie sekwencji w obwodzie logicznym.

• j niski, k high (j = 0, k = 1): Z J przy 0 i K w 1, Flip-Flop resetuje się, co powoduje, że Q jest niski (0).Ta funkcja resetowania jest poważna w systemach, które muszą powrócić do stanu domyślnego, na przykład podczas usuwania danych lub inicjowania procesu.

• Zarówno J, jak i k high (j = 1, k = 1): Gdy oba wejścia są wysokie, Flip-Flop przełącza swój stan.Jeśli Q jest wysoki, staje się niski, a jeśli Q jest niski, przełącza się na wysokie.To przełączające zachowanie jest istotne dla urządzeń, które muszą naprzemiennie stany, takie jak dzielniki częstotliwości lub liczniki.

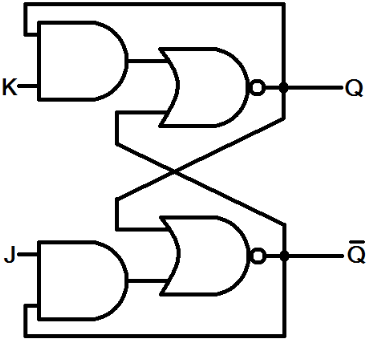

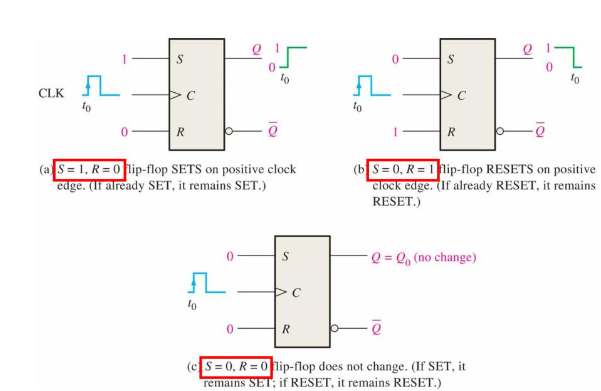

Rysunek 3: Zatrzęcanie JK

Wgląd w operację zatrzasku JK

Zatrzęcie JK działa podobnie jak Flip-Flop JK, ale bez potrzeby sygnału zegara.Zamiast czekać na krawędź zegara, zatrzask JK reaguje stale na zmiany wejściowe, co czyni ją „wrażliwą na poziom”.Oznacza to, że dopóki dane wejściowe (J i K) są stabilne, dane wyjściowe zmienią się w czasie rzeczywistym, oferując natychmiastowe informacje zwrotne w oparciu o warunki wejściowe.

W przeciwieństwie do wywołanego przez krawędzi JK Flip-Flop, który aktualizuje swoje wyjście tylko wtedy, gdy sygnał zegara zmienia się (od niskiego do wysokiego lub odwrotnie), zatrzask JK natychmiast dostosowuje swoje wyjście jako przesunięcie wejściowe.Ta stała reaktywność w czasie rzeczywistym jest cenna w scenariuszach, w których natychmiastowe działanie jest pożądane bez opóźnienia spowodowane synchronizacją zegara.

Filtry hałasu: W obwodach cyfrowych, które muszą szybko odfiltrować niechciany szum, natychmiastowa jest natychmiastowa reakcja JK zatrzasku na zmiany wejściowe.Ponieważ nie czeka na impuls zegara, może dostosować wyjście, gdy tylko hałas zostanie wykryty, zapobiegając opóźnieniu w korekcie sygnału.

Proste elementy pamięci: Zatrzęcanie JK może służyć jako podstawowa jednostka pamięci w systemach, które nie wymagają złożonej, zegarowej kontroli.Ponieważ zatrzask utrzymuje stabilność wyjściową, o ile dane wejściowe nie zmieniają się, skutecznie utrzymuje bieżący stan, co jest przydatne w przypadku obwodów wymagających przechowywania informacji bez kosztów ogólnych operacji.

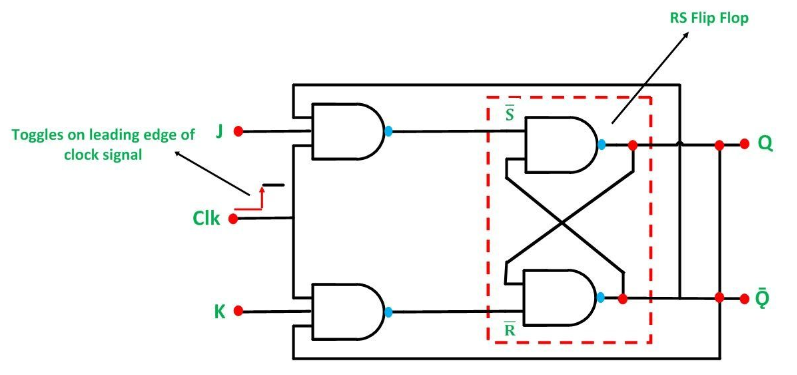

Rysunek 4: Analiza schematu czasowego dla Flip-Flop JK

Analiza schematu czasowego JK Flip-Flops

Schemat czasowy Flip-Flop JK zapewnia wizualny rozkład reakcji wyjścia na różne wejścia, zsynchronizowane z przejściami impulsu zegara.Ten schemat pokazuje związek między sygnałem zegara (CLK) a wejściami (J i K) oraz w jaki sposób wpływają one na wyniki (Q i Q ').Pomaga zmapować zachowanie Flip-Flop w stanach sekwencyjnych, ułatwiając zrozumienie jego działania.

Po pierwsze, schemat Podświetla się, że wyjścia są aktualizowane tylko na rosnących lub spadających krawędziach impulsu zegara.Ta funkcja, znana jako wyzwalanie krawędzi, dominuje w operacji JK Flip-Flop.Pokazuje, że nawet jeśli wejście J i K zmieniają się, wyjście pozostaje niezmienione, aż do wystąpienia krawędzi zegara, zapewniając przewidywalne i stabilne przejścia.

Następnie, gdy schemat mapuje zmiany wejściowe j i k, wizualnie Pokazuje, w jaki sposób każda kombinacja wejściowa wpływa na wyjście. Na przykład, gdy zarówno J, jak i K są niskie (0), dane wyjściowe utrzymuje swój obecny stan.Gdy J jest wysokie, a K jest niski, wyjście jest ustawione.Ta wyraźna wizualna reprezentacja pomaga zrozumieć, jak reaguje Flip-Flop na różne kombinacje wejściowe w czasie rzeczywistym.

Wreszcie, Schemat taktowania wyraźnie pokazuje przejścia między różnymi stanami wyjściowymi, czy to trzymanie, ustawienie, resetowanie lub przełączanie.Każda zmiana stanu jest powiązana bezpośrednio z warunkami wejściowymi i krawędzią zegara, pokazując związek przyczynowo-skutkowy, który jest ogniskowy dla obwodów projektowania i rozwiązywania problemów.

Wszechstronne zastosowania klapek JK

Flip-klapy JK są podstawowymi komponentami w szerokim zakresie systemów cyfrowych, znanych ze swojej elastyczności i niezawodności.Ich zdolność do obsługi złożonych operacji logicznych sprawia, że są wymagane w kilku kluczowych aplikacjach, w tym:

Rysunek 5: Pamięć pamięci

Flip-klapy JK są powszechnie używane do przechowywania poszczególnych bitów danych, co czyni je podstawowymi elementami w tablicach pamięci i rejestrach.Każdy flip-flop trzyma jeden bit, zapewniając niezawodne przechowywanie danych, co jest korzystne w projektowaniu większych systemów pamięci.

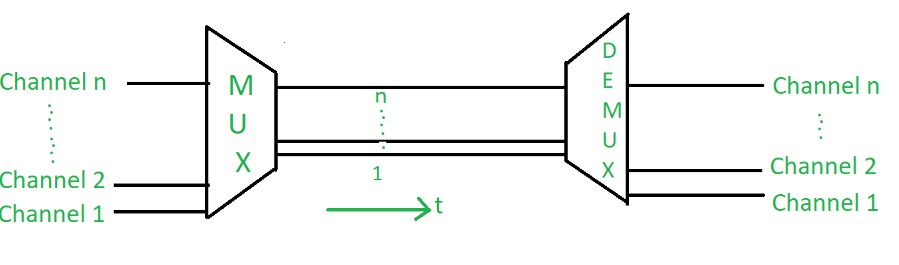

Rysunek 6: Rejestry kontrataków i zmian

Flip-klapy JK są dynamiczne w operacjach sekwencjonowania.Są one szeroko stosowane w licznikach do zliczania zdarzeń lub impulsów oraz w rejestrach zmian do przekształcania danych szeregowych w formaty równoległe.To sprawia, że są przydatne w zarządzaniu danymi i manipulowaniu danymi na różnych etapach procesu, na przykład w systemach komunikacyjnych.

Rysunek 7: Podział częstotliwości

Podczas przetwarzania sygnału JK Flip-Plops są często używane do podziału częstotliwości.Przełączając swój stan z każdym impulsem zegara, dzielą częstotliwość sygnału wejściowego, tworząc wolniejszy, łatwiejszy do opanowania sygnał zegara.Jest to godne uwagi w aplikacjach takich jak zarządzanie sygnałami zegara, w których pożądana jest kontrola czasu.

Rysunek 8: Synchronizacja

JK Flip-Flops pomaga synchronizować wiele procesów cyfrowych, zapewniając, że różne części systemu działają razem w skoordynowany sposób.Zapewniają, że różne komponenty reagują poprawnie na sygnały czasowe, utrzymując synchronizację całego systemu.

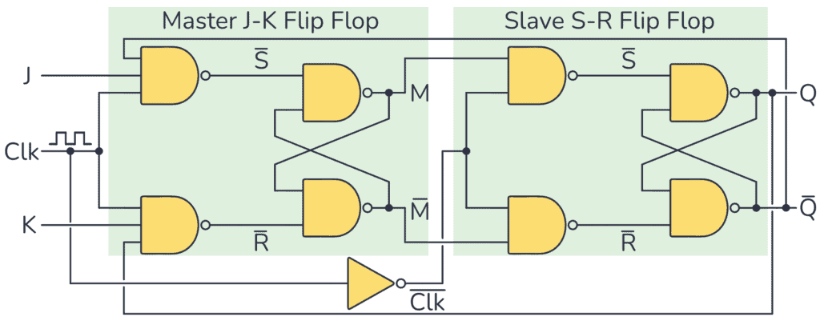

Rysunek 9: Flip-Flop JK: wyzwalany krawędź i wyzwalany na poziomie

Różne rodzaje klapek JK

Flip-klapy JK są dostępne w dwóch głównych typach: wyzwalanych krawędzi i wyzwalaniu poziomu, z których każda zaprojektowana dla różnych wymagań operacyjnych.

Wykonane z krawędzi JK Flip-Flops: Zmień swój stan tylko w określonych punktach - gdy sygnał zegara przechodzi z niskiego do wysokiego (wznoszącej się krawędzi) lub wysokiej do niskiej (krawędź spadająca).Ta cecha sprawia, że idealnie nadają się do systemów, w których naleganie jest precyzyjne czas.Ponieważ zmiany stanu występują dokładnie na krawędzi zegara, te odwrotne flopy zapewniają, że wszystkie aktualizacje mają miejsce zsynchronizowane z impulsem zegara.To przewidywalne zachowanie jest dynamiczne w ściśle kontrolowanych środowiskach, takich jak zegary cyfrowe, rejestry i większość obwodów sekwencyjnych.Tutaj czas każdej zmiany jest poważny dla utrzymania stabilności systemu i zapewnienia synchronizacji operacji.

Wykonane poziomy JK Flip-Flops: Działaj inaczej, reagując na sygnał wejściowy, o ile sygnał zegara jest na określonym poziomie - niezależnie od wysokiego czy niskiego.Nie czekają na określone przejście zegara.Zamiast tego, dopóki wejście spełnia wymagane warunki, Flip-Flop zmieni stany.To zachowanie sprawia, że wyzwalane poziomy Flip-klapy są lepsze dla systemów asynchronicznych, w których wejścia mogą nie wyrównać z zwykłym impulsem zegara.Zapewniają one elastyczność w systemach, w których dane wejściowe są nieprzewidywalne lub osiągają nieregularne odstępy, na przykład w niektórych zadaniach przetwarzania sygnałów lub systemach monitorowania, które muszą natychmiast zareagować na zmieniające się dane wejściowe.

Plusy i wady JK Flip-Flop

Flip-klapy JK oferują kilka korzyści, ale są również wyposażone w niektóre kompromisy, które należy dokładnie zważyć przy projektowaniu systemów cyfrowych.

|

Profesjonaliści |

|

|

Wszechstronność |

Flip-klapy JK są bardzo elastyczne i mogą

być używane w różnych obwodach cyfrowych, takich jak pamięć pamięci, liczniki i

systemy sterowania.Mogą przełączać, ustawić lub zresetować na podstawie różnych wejść

warunki, dzięki czemu są odpowiednie do szerokiej gamy zastosowań

Wymagaj precyzyjnej kontroli nad przejściami stanu. |

|

Mechanizm samokontrolujący |

Jedna z wyróżniających się funkcji JK

Flip-Flops to ich wbudowana pętla sprzężenia zwrotnego, która pomaga poprawić logiczne

stany dynamicznie.Ta samowystarczalność zapewnia, że obwód pozostaje

stabilne podczas pracy, nawet gdy dane wejściowe zmieniają się szybko. |

|

Łagodzenie stanu rasy |

W przeciwieństwie do prostszych klapek, Flip-Flops JK

są zaprojektowane w celu zapobiegania warunkom wyścigowym - wyniki, w których staje się produkcja

niestabilne ze względu na sprzeczne sygnały wejściowe.Ta zdolność do utrzymania

spójne wyjście, nawet przy szybkich i sekwencyjnych zmianach wejściowych, poprawia

niezawodność obwodu. |

|

Wady |

|

|

Złożony projekt |

Flip-klapy JK są bardziej skomplikowane niż

Podstawowe klapki.Ich konstrukcja wymaga dodatkowych bram logicznych i danych wejściowych

Monitorowanie, które może utrudnić zaprojektowanie obwodu i

Rozwiązywanie problemów, szczególnie w systemach, w których preferowana jest prostota. |

|

Opóźnienie propagacji |

Bramowanie wewnętrzne używane do zarządzania stanem

Przejścia wprowadza opóźnienie w tym, jak szybkie sygnały mogą być przetwarzane.W

Aplikacje szybkie, to opóźnienie może wpływać na ogólny czas i spowolnić

Wydajność obwodu. |

|

Wyższe zużycie energii |

Ze względu na ich złożoność i potrzebę

stale monitoruj warunki wejściowe, JK Flip-Flops zużywają więcej mocy

w porównaniu do prostszych klapek.W większych systemach lub wrażliwych na moc

Zastosowania, ten wyższy zapotrzebowanie na moc może stać się wadą |

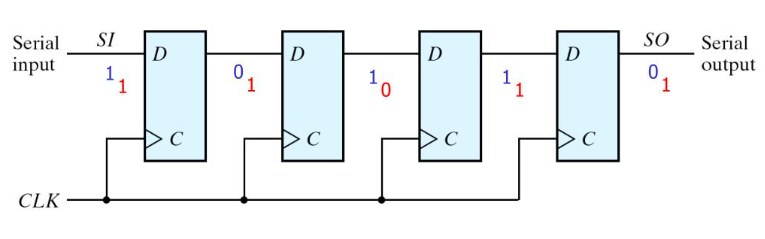

Rysunek 10: Flip-flop JK Master-Slave

Dekodowanie mistrza JK Flip-flop

Master-Slave JK Flip-Flop został zaprojektowany w celu rozwiązania stanu wyścigowego występującego w standardowych flip-flopach JK za pomocą dwuetapowego procesu do bardziej wydajnego zarządzania wejściami i wyjściami.

Pierwszy etap, zwany etapem głównym, rejestruje wartości wejściowe, gdy sygnał zegara osiąga określoną krawędź, wznoszącą lub spadającą.W tym momencie dane wejściowe są zablokowane, co oznacza, że dalsze zmiany wejściowe nie wpływają na stan przechwycony do następnego cyklu zegara.Ten etap zapewnia, że Flip-Flop rejestruje prawidłowe dane wejściowe, nie wpływając na żadne późniejsze zmiany w tym samym cyklu zegara.

Po zakończeniu sceny głównej wchodzi scena niewolników.Ten etap aktualizuje dane wyjściowe na podstawie danych przechwyconych przez etap główny, ale tylko na następnej krawędzi zegara.Oddzielając przechwytywanie wejściowe od aktualizacji wyjściowej, etap niewolnika zapewnia, że wyjście pozostaje stabilne, dopóki etap główny w pełni przetworzy wejście.Zapobiega to przedwczesnym lub niezamierzonym zmianom wyjściowej w cyklu zegara.

Dlaczego liczy się konfiguracja mistrza niewolnika?

Dwustopniowy proces stabilizuje działanie Flip-Flop JK, zapobiegając niechcianym oscylacji lub fluktuacji, które mogą nastąpić w prostszych konfiguracjach, szczególnie gdy oba dane wejściowe są wysokie.Odsprzężając przetwarzanie wejściowe od zmiany wyjściowej, konfiguracja mistrza niewolnika zapewnia, że wyjścia pozostają przewidywalne i stabilne, nawet w sytuacjach, w których czas jest cenny.

Zwracanie się do wyścigu wokół stanu w Flip-Flops JK

Warunki wyścigowe występują w klapkach JK, gdy oba wejścia, J i K, są wysokie, a sygnał zegara pozostaje aktywny zbyt długo.Prowadzi to do ciągłego przełączania wyjść, co może powodować nieregularne zachowanie i zakłócać wiarygodność obwodu.

Konfiguracja Master-Slave wykorzystuje dwustopniowy proces, aby zapobiec problemom z wyścigiem.Etap główny przechwytuje wartości wejściowe na krawędzi zegara i blokuje je. Etap niewolnika aktualizuje wyjścia przy następnej krawędzi zegara, zapewniając, że wyjście nie zmieni się, dopóki wejścia zostaną w pełni przetworzone.Takie podejście skutecznie zapobiega niekontrolowanym przełączeniu wyjścia, nawet jeśli dane wejściowe pozostają wysokie przez dłuższy czas.

Inną metodą unikania warunków wyścigowych jest regulacja czasu trwania impulsu zegara.Dzięki temu impulsowi zegara krótszego niż opóźnienie propagacji Flip-Flop, możesz upewnić się, że stan nie zmieni się więcej niż raz w tym samym cyklu zegara.Zapobiega to wielokrotnym przełączaniu Flip-Flop podczas jednego cyklu, stabilizując wyjście.

Dynamika przełączania w klapkach JK

Zachowanie przełączania Flip-Flop JK jest w dużej mierze napędzane przez czas sygnału zegara i poziomów wejściowych (J i K).Stan zmienia Flip-Flop w oparciu o wejścia obecne na dodatniej krawędzi sygnału zegara.W tym niebezpiecznym momencie Flip-Flop ocenia dane wejściowe i odpowiednio aktualizuje swoje dane wyjściowe.

Gdy sygnał zegara uderza w wznoszącą się krawędź, JK Flip-Flop odczytuje bieżące stany wejść J i K.W zależności od ich wartości Flip-Flop będzie albo przytrzymywać, ustawić, zresetować lub przełączać swoje wyjście.

Cyfrowe zegary: Dokładność jest wszystkim w cyfrowych zegarach, a klapki JK pomagają utrzymać tę precyzję, zapewniając, że zmiany stanu występują tylko w precyzyjnych odstępach czasu.

Sekwencyjne testery logiczne: W systemach testujących funkcjonalność obwodów logicznych JK Flip-Flops odgrywają rolę w sprawdzaniu, czy każdy komponent poprawnie reaguje na określone sygnały czasowe.

Inne systemy wrażliwe na czas: W różnych aplikacjach cyfrowych, w których czas jest ryzykowny, takie jak systemy komunikacji lub jednostki przetwarzania danych, JK Flip-Flop zapewnia, że przejścia stanu występują zsynchronizowane z zegarem, zapobiegając błędom pomiaru czasu.

Wniosek

JK Flip-Flop wyróżnia się jako ostateczny element w projektowaniu obwodów cyfrowych, oferując mieszankę wszechstronności i precyzji desperackiej dla szerokiej gamy aplikacji, od przechowywania pamięci po podział częstotliwości i synchronizację procesów cyfrowych.Jego zdolność do łagodzenia warunków wyścigowych poprzez innowacyjne konfiguracje, takie jak aranżacja mistrza niewolnika, podkreśla jego zdolność adaptacyjną w rozwiązywaniu nieodłącznych wyzwań projektowych.Podobnie, poważna rola Flip-Flop w zapewnieniu precyzyjnych przejść stanu podkreśla jego wymagany charakter w tworzeniu i utrzymaniu niezawodnych i wydajnych systemach cyfrowych.W miarę postępu technologii ewoluujące projekty i zastosowania JK Flip-Flop są nadal kluczowe w przekraczaniu granic cyfrowej elektroniki w kierunku bardziej wyrafinowanych i solidnych architektur.

Często zadawane pytania [FAQ]

1. Jakie są zastosowania Flip Flip JK?

Flip-flop JK jest szeroko stosowany w cyfrowej elektronice do różnych zadań:

Aplikacje rozrządu: Może służyć jako element opóźnienia lub timer po podłączeniu w niektórych konfiguracjach.

Liczniki i rejestry: Przełączając swój stan z każdym impulsem zegara, jest używany do projektowania różnych liczników i rejestrów zmian, które są ostateczne w sekwencyjnych obwodach logicznych.

Pamięć: Zapewnia podstawową jednostkę przechowywania pamięci, przydatna w przechowywaniu bitów w aplikacjach obliczeniowych.

2. W jaki sposób JK Flip-Flop działa z tabelą prawdy?

Flip-flop JK ma dwa wejścia (J i K) i sygnał zegara.Jego działanie różni się w zależności od stanów wejściowych, zsynchronizowanych z zegar:

• J = 0, K = 0: Wyjście się nie zmienia.

• J = 0, K = 1: Wyjście resetuje się do 0.

• J = 1, K = 0: Wyjście jest ustawione na 1.

• J = 1, k = 1: Wyjście (tj. Jeśli było to 0, staje się 1 i odwrotnie).

3. Co to jest Flip Flip i czy to działa?

Flip-flop JK łączy właściwości klapek SR i T.Unika stanu „zabronionego” widocznego w klapkach SR za pomocą wejść JK skutecznie:

Stan Flip-Flop jest kontrolowany przez wejścia J i K, które określają, czy wyjście powinno przytrzymać, zresetować, ustawić lub przełączać, zsynchronizując się z podnoszącą lub spadającą krawędzią impulsu zegara.

4. Jakie są zastosowania zatrzasków i klapek?

Przechowywanie danych: Zatrzęcie i klapki są poważne dla przechowywania danych w rejestrach i macierzy pamięci.

Dział częstotliwości: Stosowane w dzielnikach częstotliwości ze względu na ich zdolność do zmiany stanów na krawędziach zegarowych, zmniejszając o połowę częstotliwość z każdym etapem w serii.

Maszyny stanowe: Podstawowe w projektowaniu skończonych maszyn stanu, które są używane do wdrażania sekwencyjnych obwodów logicznych i kontrolnych.

Debuin: Służy do stabilizacji sygnałów z mechanicznych przełączników i przycisków, zapewniając pojedyncze, czyste przejścia.

5. Do czego są używane klapki?

Przechowywanie binarne: Każdy flip-flop przechowuje jeden kawałek danych, co czyni je elementami składowymi dla binarnych urządzeń do przechowywania.

Podziałowie zegara: Dzielą częstotliwość zegara wejściowego przez dwa, przydatne w zegarach cyfrowych i aplikacjach czasowych.