T Przewodnik dla wiedzy wyzwala - zalety i wady, jak to działa, typy

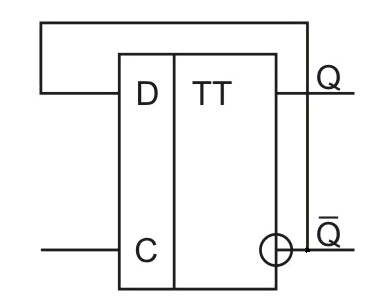

Flopy T są podobne do klapek JK.Łącząc dane wejściowe J i K, można wyprowadzić Flip-Flop.Podobnie jak Flip-Flop, ma tylko jedno wejście zewnętrzne wraz z zegar.

Katalog

Jak działają flopy T

klapki są najprostszymi urządzeniami w automatach cyfrowych, wykazujące dwa stabilne stany.Jeden stan ma wartość „1”, a drugie „0” ”Stan urządzenia i przechowywane w nim informacje binarne są określane przez sygnały wyjściowe: bezpośredni i odwrotny.Jeśli potencjał jest ustawiony na bezpośrednim wyjściu odpowiadającym wyjściu logicznym, urządzenie jest w stanie pojedynczego wyzwalania (potencjał odwrotnego wyjścia odpowiada logicznej zero).Jeśli nie ma potencjału na wyjściu bezpośredniej, urządzenie znajduje się w stanie zerowym.

Rodzaje flopów T

Flopy T są przede wszystkim w dwóch odmianach:

Asynchroniczny wyzwalacz T.

Synchroniczny wyzwalacz T.

Oba rodzaje flopów T działają podobnie.Jedyną różnicą jest proces przejścia z jednego stanu do drugiego.Typ asynchroniczny wykonuje to przejście bezpośrednio, podczas gdy typ synchroniczny działa na podstawie tego sygnału.

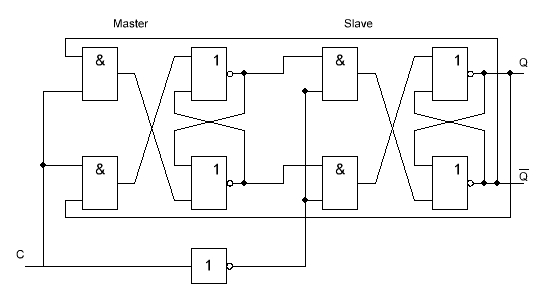

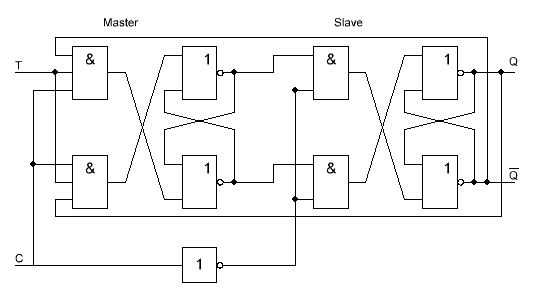

Podczas oceny scenariusza, w którym wejście zegara jest zawsze wysokie (1), należy wziąć pod uwagę dwa potencjalne stany wejścia (t), wysokie (1) lub niskie (0).Podajmy wyniki dla każdego stanu i zaangażowanych interakcji bramy logicznej.

Przypadek 1: t = 0

- Warunek wyjściowy: Tutaj zarówno brama1, jak i brama 2 są podłączone do t (ustawione na 0).

- Wyjście Gate1 i Gate2: Ponieważ wyjściowe wyjście bramki 0, gdy którekolwiek z jej wejść wynosi 0, wyjścia bramki 1 i bramki 2 będą zawsze wynosić 0, niezależnie od innych wejść.

- GATE3/Q (N+1) Logika: Brama3 ma wpływ wyjście bramki1.Gdy Gate1 wysyła 0, równanie logiczne GATE3 upraszcza (0 lub nie Q), co skutkuje Q.

- GATE4/Q (N+1) „Logika: brama4 jest zgodny z podobnym wzorem, wytwarzając nie (0 lub q), upraszczając do nie Q lub Q '.

Podsumowanie przypadku 1:

- Zakładając bramę1 = 0 i bramę 2 = 0, i wykorzystując charakterystykę i bramy (dowolne wejście 0 powoduje wyjście 0), operacja jest prosta:

- GATE3/Q (N+1) oblicza się jako Q, utrzymując bieżący stan.

- GATE4/Q (N+1) „powoduje q”, uzupełnienie obecnego stanu.

Przypadek 2: t = 1

- Warunek wyjściowy: Gdy t jest ustawione na 1, wejścia bramki 1 i GATE2 odzwierciedlają teraz wyjścia innych operacji logicznych, wpływając na ich wyjścia.

- Wyjście Gate1 i Gate2: GATE1 łączy się bezpośrednio z bieżącym stanem Q, a GATE2 z nie Q lub Q '.

- GATE4/Q (N+1) „Logika: Tutaj równanie upraszcza, ponieważ wejścia bramki są przeciwieństwami (q i nie q), co daje 0.

- GATE3/Q (N+1) Logika: Z drugiej strony Gate3 zajmuje się nie Q lub Q ', nie wysyłając (Q i 0), upraszczając nie Q lub Q'.

Podsumowanie przypadku 2:

- Konfiguracja logiczna prowadzi do interesujących interakcji:

- GATE1 = Q, GATE2 = Q ', wpływając na kolejne procesy logiczne.

- GATE4/Q (N+1) „Bezpośrednio oblicza się jako 0, ponieważ i działanie między Q a nie Q nie może być prawdziwe.

- Gate3/Q (n+1) następnie oblicza jako q ', czyli przełącznik z poprzedniego stanu, gdy t wynosił 0.

T Flip-Flop Tabel

|

Clk |

T |

Q (n+1) |

Państwo |

|

|

0 |

Q |

Bez zmiany |

|

|

1 |

Q' |

DŹWIGNIA KOLANKOWA |

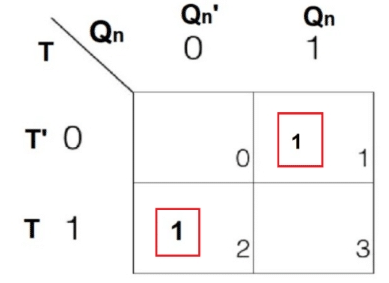

Użyjemy tej tabeli prawdy, aby skompilować charakterystyczną tabelę dla flop-flop.W tabeli prawdy możesz zobaczyć tylko jedno wejście t i jedno wyjście Q (n+1).Jednak w tabeli charakterystycznej zobaczysz dwa wejścia T i QN oraz jedno wyjście Q (N+1).

Z powyższego schematu logicznego jasne jest, że QN i QN 'są dwoma komplementarnymi wyjściami, również działającymi jako wejścia dla bramy3 i bramy4, dlatego uważamy QN (tj. Obecny stan flip-flopa) za wejście i q ((n+1) jako wyjście dla następnego stanu.

Po ukończeniu tabeli charakterystycznej skonstruujemy 2-zmienną mapę K, aby wyprowadzić charakterystyczne równanie.

|

T |

Qn |

Q (n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0

|

Z mapy K otrzymasz dwie pary.Rozwiązując oba, otrzymujemy następujące równanie charakterystyczne:

Q (n + 1) = tqn ’ + t’qn = t xor qn

Zalety korzystania z flopów T

W obwodach cyfrowych flopy T oferują kilka istotnych korzyści, które upraszczają ich funkcję i integrację:

- Jedno wejściowe prostota: Flopy T mają tylko jedno dane wejściowe, upraszczając ich działanie.To pojedyncze wejście może przełączać się między stanami wysokimi i niskimi, umożliwiając bezproblemowe integrację z projektami obwodów i łatwe połączenie z innymi obwodami cyfrowymi.

- Brak nieprawidłowych stanów: Flopy T nie mają nieprawidłowych stanów, pomagając zapobiegać nieprzewidywalnym zachowaniu w systemach cyfrowych.Ta niezawodność ma kluczowe znaczenie dla utrzymania spójnej wydajności systemu.

- Zmniejszone zużycie energii: W porównaniu z innymi klapkami, flopy T zużywają mniejszą moc.Ta efektywność energetyczna jest korzystna dla rozszerzenia żywotności baterii urządzeń przenośnych i zmniejszenia kosztów energii dużych systemów cyfrowych.

- Operacja bistabilna: Podobnie jak inne klapki, flopy T-FLIP-FLOPS mają działanie bistabilne, co oznacza, że mogą one w nieskończoność utrzymywać stan (0 lub 1), aż do uruchomienia sygnałem wejściowym.Ta charakterystyka jest niezbędna dla aplikacji wymagających stabilnego, długoterminowego przechowywania danych jednobitowych.

- Łatwa wdrożenie: Flopy T można łatwo zaimplementować za pomocą podstawowych bram logicznych.Ta prostota sprawia, że są one opłacalnym ekonomicznie wyborem dla wielu systemów cyfrowych, pomagając obniżyć ogólne koszty systemu.

Ograniczenia flopów T

Pomimo tych zalet, flopy T mają również pewne ograniczenia, które mogą wpływać na ich przydatność do niektórych aplikacji:

- Odwrócone wyjście: Wyjście flopów T jest przeciwieństwem jego wejścia, co może komplikować konstrukcję obwodów logicznych czasowych i uczynić projekt bardziej złożonym.Projektanci muszą to rozważyć, aby zapewnić prawidłowe zachowanie obwodu.

- Ograniczona funkcjonalność: Flopy T mogą przechowywać tylko jedną informację i nie są w stanie wykonywać złożonych operacji, takich jak dodawanie lub mnożenie, ograniczając ich użycie w podstawowych zadaniach pamięci.

- Wrażliwość na usterki: Flopy T-flips mogą być wrażliwe na usterki i szum w sygnale wejściowym, potencjalnie powodując nieoczekiwane zmiany stanu.Ta wrażliwość może prowadzić do nieprzewidywalnego zachowania w systemach cyfrowych, szczególnie w środowiskach o wysokich zakłóceniach elektronicznych.

- Opóźnienie propagacji: Podobnie jak wszystkie klapki, opóźnienia propagacji flopów T, które mogą wprowadzać problemy czasowe w systemach o ścisłych ograniczeniach czasowych.Opóźnienia te należy wziąć pod uwagę podczas projektowania systemu, aby uniknąć błędów czasowych i zapewnić niezawodne działanie.

Zastosowania

Flopy T są używane w różnych aplikacjach w świecie rzeczywistym, w tym:

- Dział częstotliwości: Flopy T-flips są często używane do zmniejszenia o połowę częstotliwości sygnału zegara.Przełączając stan Flip-Flop z każdym impulsem zegara, skutecznie dzielą częstotliwość sygnału wejściowego przez dwa, czyniąc je idealnymi do precyzyjnych czasów i cyfrowych zegarów i syntezy częstotliwości.

- Podwojenie częstotliwości: I odwrotnie, flopy T mogą być również użyte do podwojenia częstotliwości sygnału zegara, znanego jako podwojenie częstotliwości.Osiąga się to poprzez konfigurację klapek w konfiguracji, która generuje częstotliwość wyjściową dwukrotnie większą niż sygnał wejściowy.

- Przechowywanie danych: Flopy T-flip mogą być używane jako podstawowe elementy składowe do przechowywania bitów pojedynczych danych, w których dane muszą być tymczasowo zapisane w celu dalszego przetwarzania lub transmisji.To czyni je bardzo przydatnymi w aplikacjach, takich jak rejestry zmiany i urządzenia pamięci masowej.

- Liczniki: Innym znaczącym zastosowaniem flopów T jest tworzenie liczników binarnych.Można je powiązać z innymi cyfrowymi bramkami logiki w celu konstruowania liczników, które mogą zwiększyć lub zmniejszać w zależności od wymagań projektowych.