Opanowanie zatrzasków SR: Symbole, funkcje i praktyczne zastosowania

Zatrzask SR to obwód asynchroniczny, który działa niezależnie od sygnałów zegara, co czyni go wszechstronnym narzędziem w różnych aplikacjach.Utrzymuje stan binarny - albo wysoki (1) lub niski (0) - i może przechowywać pojedynczą informację, którą utrzymuje, dopóki nowe sygnały wejściowe nie podkają zmiany.Ten podstawowy element przechowywania binarny jest konstruowany przy użyciu dwóch bramek logicznych, zwykle ani bramek NAND.Ustaw wejścia (y) aktywuje zatrzask, ustawiając wyjście (q) na wysokie, podczas gdy wejście reset (R) ustawia wyjście na niski poziom.Jednak jednoczesne wysokie sygnały na obu danych wejściowych prowadzą do stanu niezdefiniowanego, muszą unikać projektanci stanu.Zatrzęcie SR to nie tylko konstrukty teoretyczne;Są one wdrażane w systemach praktycznych w celu przechowywania danych tymczasowych, obsługi pośredniego przetwarzania, a nawet zarządzania wykrywaniem błędów w krytycznych aplikacjach, takich jak lotniska i urządzenia medyczne, pokazując ich niezbędność w projektowaniu obwodów cyfrowych.Katalog

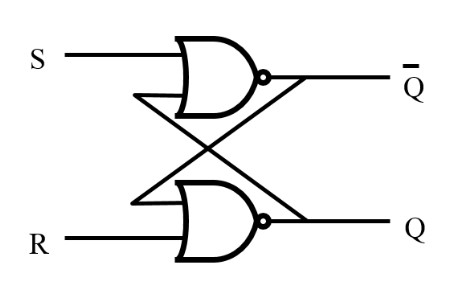

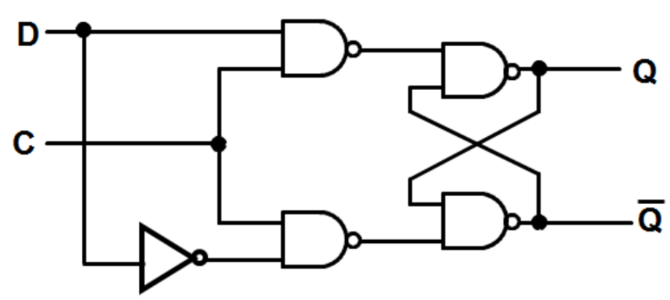

Rysunek 1: Zatrzask SR

Co to jest zatrzask SR?

Zatrzask SR lub zatrzask set-reset to podstawowy element magazynowy binarny, który należy do kategorii obwodów asynchronicznych.W przeciwieństwie do obwodów synchronicznych, zatrzaski SR działają bez sygnału zegara, polegając wyłącznie na bezpośredniej kontroli sygnałów wejściowych.Pozwala im to funkcjonować niezależnie w obwodach cyfrowych.Zatrzask SR może utrzymać dwa stabilne stany: wysokie (1) i niskie (0), umożliwiając mu przechowywanie pojedynczych informacji, dopóki nie zostanie zaktualizowany przez nowe sygnały wejściowe.

Konstruowanie zatrzaski SR zwykle obejmuje dwie bramki logiczne, powszechnie ani bramy lub bramy NAND.W konstrukcji zatrzasku SR przy użyciu bramek, wyjście każdej bramki jest podłączone do wejścia drugiej, tworząc pętlę sprzężenia zwrotnego.Ta konfiguracja zapewnia, że zatrzask może szybko zmienić stany na podstawie sygnałów wejściowych przy jednoczesnym zachowaniu stabilności, dopóki nowy wejście nie wyruszy w błąd.

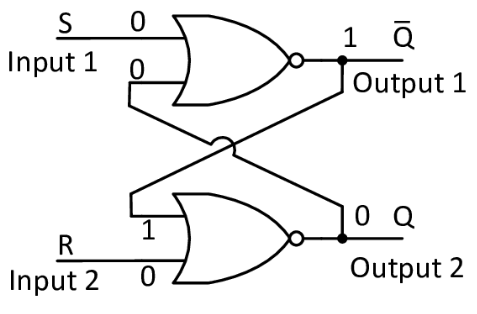

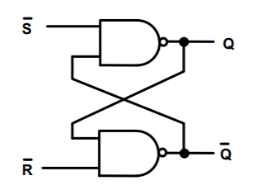

Rysunek 2: Zatrzask SR (2)

Ustaw wejścia (y): Gdy ustawienie wejściowe (S) są aktywowane (wysokie), wyjście zatrzasne (q) przełącza się na wysokie (1).

Zresetuj wejście (R): Gdy wejście resetowania (R) jest aktywowane (wysokie), wyjście (Q) przełącza się na niski (0).

Oba wejścia wysokie: jeśli oba wejścia S i R są wysokie jednocześnie, zatrzask wchodzi w nieokreślony stan, którego należy unikać w projektowaniu.

Zatrzymania SR są niezbędne do tymczasowego przechowywania danych i pośrednich wyników w systemach cyfrowych.Są to podstawowe elementy w bardziej złożonych obwodach sekwencyjnych, takich jak wielobitowe rejestry zmiany, jednostki pamięci i niektóre typy liczników.

W tych aplikacjach zatrzaski SR zapewniają stabilną retencję danych i mogą szybko reagować na zmiany sygnałów zewnętrznych, zapewniając wydajne działanie całego systemu elektronicznego.

Kolejnym krytycznym zastosowaniem zatrzasków SR jest wykrywanie błędów i logika korekcji w obwodach cyfrowych.Ze względu na zdolność do utrzymania stanu stabilnego mogą monitorować zmiany statusu systemu i szybko powrócić do predefiniowanego bezpiecznego stanu po wykryciu anomalii.Ta funkcja jest szczególnie cenna w systemach o wysokiej niezawodności, takich jak lotniska i urządzenia medyczne.

Symbol zatrzasku SR

Zrozumienie jego symbolu i struktury ma fundamentalne znaczenie dla uchwycenia jego działania i praktycznego zastosowania.W schematach obwodów zatrzask SR zwykle ma dwa główne porty wejściowe oznaczone S (SET) i R (RESET).Te wejścia kontrolują stan wyjściowy zatrzasku, powszechnie reprezentowany jako Q. Niektóre projekty zawierają również odwrotne wyjście, oznaczone Q ', które zapewnia przeciwny stan Q.

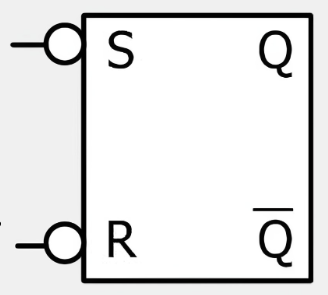

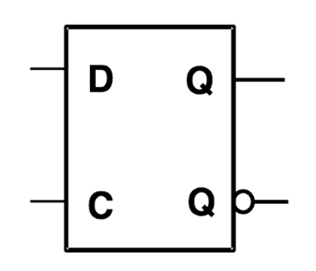

Rysunek 3: Symbol zatrzasku SR

Zatrzask SR jest często reprezentowany przez prostokątny symbol z wejściami S i R oraz wyjściem Q. W niektórych przypadkach pokazano również wyjście Q '.To wyraźne etykietowanie pozwala projektantom obwodów szybko zidentyfikować funkcję komponentu i jego rolę w większym obwodzie.

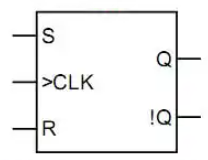

Wspólny wariant zatrzasku SR obejmuje wejście zegara (CLK).Wejście CLK zapewnia, że zmiany stanu występują w synchronizacji z sygnałem zegara, umożliwiając dokładną kontrolę czasu.W tej konfiguracji, nawet jeśli S lub R są aktywowane, stan zatrzasny aktualizuje się tylko wtedy, gdy sygnał CLK spełnia określone warunki, zwykle na wznoszącym się lub spadającym krawędzi.Zapobiega to błędom spowodowanym usterkami sygnałowymi lub niezamierzonymi zmianami.

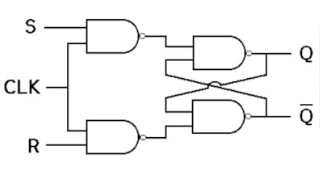

Rycina 4: Symbol bramkowanego zegarów SR

Symbol zatrzasny SR zawiera wejścia S, R i CLK wewnątrz prostokąta.Ta znormalizowana reprezentacja pomaga projektantom zrozumieć funkcjonalność zatrzasku i jej wymagania dotyczące pomiaru czasu.Na przykład w wysokowydajnych systemach obliczeniowych lub złożonych systemach transferu danych ostrożna kontrola CLK zapewnia przechowywanie i przesyłanie danych na każdym etapie przetwarzania, optymalizując ogólną wydajność i niezawodność systemu.

Dokładna kontrola wejściowych zatrzasków SR jest ważna, szczególnie przy projektowaniu pamięci o dużej prędkości i o dużej pojemności lub tymczasowych buforach danych.Dzięki projektowaniu obwodów logicznych w celu zarządzania aktywacją S i R można osiągnąć złożone funkcje, takie jak ładowanie danych, usuwanie lub resetowanie stanu.Dokładna kontrola sygnału CLK zapewnia, że wszystkie operacje danych są zgodne z predefiniowaną sekwencją taktowania, znacznie zwiększając wydajność systemu i możliwości przetwarzania danych.

Głębokie zrozumienie symbolu i struktury zatrzasku SR pomaga nie tylko w prawidłowym projektowaniu i rozwiązywaniu problemów, ale także w wykonywaniu złożonych operacji logiki cyfrowej i poprawie wydajności systemu.Jest to szczególnie kluczowe w aplikacjach wymagających wysokiej niezawodności i precyzyjnej kontroli, takich jak lotniska i urządzenia medyczne.

Rodzaje zatrzasków i ich zasady pracy

Zatrzęcie są podstawowymi komponentami w projektowaniu elektronicznym, oferując różnorodne funkcje i szerokie zastosowania.Główne typy zatrzasków to zatrzaski SR i zatrzaski D, każda z unikalnymi operacjami i przypadkami użycia.

SR Latch

Zatrzask SR lub zatrzask Set-Reset to podstawowe urządzenie pamięci kontrolowane przez dwa wejścia, S (SET) i R (RESET).

Gdy wejście S odbiera wysoki sygnał, wyjście Q staje się wysokie, wskazując, że dane są ustawione.Gdy wejście R odbiera wysoki sygnał, wyjście Q staje się niskie, wskazując, że dane są resetowane.Jeśli zarówno wejścia S, jak i R są wysokie jednocześnie, zatrzask wchodzi w nieokreślony stan, powodując potencjalną niestabilność wyjściową.Tego stanu należy unikać w projektowaniu.Bezpośrednia odpowiedź SR zatrzasku na sygnały wejściowe sprawia, że przydatne jest w sytuacjach wymagających szybkiej reakcji.

D Zatrzęcanie się

Zatrzęcanie D, znane również jako zatrzask danych lub przezroczysty zatrzask, oferuje bardziej złożoną kontrolę z wejściem danych D i sygnałem zegara CLK.

Rysunek 5: D zatrzask

Rysunek 6: D symbol zatrzasku

Gdy CLK jest wysoki, wyjście Q podąża za wejściem D, umożliwiając swobodne przechodzenie przez przelotę danych.Gdy CLK się nie ulega, bieżąca wartość D jest zablokowana, a wyjście Q pozostaje stały do następnego sygnału wysokiego CLK.Ten mechanizm sprawia, że zatrzask D jest idealny do tymczasowego przechowywania danych w celu synchronizacji różnych prędkości przetwarzania w systemie.

Zatrzęcie SR i D odgrywają niezrównaną rolę w przechowywaniu danych i logice maszyny stanu.Ze względu na bezpośrednią odpowiedź poziomu wejściowego zatrzaski są niezbędne w projektowaniu obwodów asynchronicznych.Zapewniają one istotne funkcje dla złożonych transferów danych i systemów zarządzania energią, skutecznie przechowując informacje o stanie w celu zapewnienia stabilnego działania.Właściwe użycie tych zatrzasków może znacznie poprawić niezawodność i wydajność obwodu, co czyni je niezbędnymi w nowoczesnych systemach elektronicznych.

Tabela prawdy zatrzasku SR

Rysunek 7: SR Nand zatrzask

|

S |

R |

Q |

Q' |

Notatka |

|

0 |

0 |

1 |

1 |

ZABRONIONY |

|

0 |

1 |

1 |

0 |

USTAWIĆ |

|

1 |

0 |

0 |

1 |

RESETOWANIE |

|

1 |

1 |

Q |

Q' |

ZACHOWAĆ |

Wykres 1: Tabela prawdy z zatrzasku SR za pomocą Nand Gates

Rysunek 8: Sr ani zatrzask

|

S |

R |

Q |

Q' |

Notatka |

|

0 |

0 |

Q |

Q' |

ZACHOWAĆ |

|

0 |

1 |

1 |

0 |

RESETOWANIE |

|

1 |

0 |

0 |

1 |

USTAWIĆ |

|

1 |

1 |

0 |

0 |

ZABRONIONY |

Wykres 2: Tabela prawdy z zatrzaskiem SR za pomocą ani bram

Teraz bierzemy tabelę prawdy zatrzasku SR, używając ani bramki jako przykład, aby zrozumieć znaczenie tabeli prawdy zatrzasku SR.

Stany wejściowe i wyjściowe

Zarówno S, jak i R wynoszą 0: Zatrzmieć pozostaje w obecnym stanie.Wyjście Q pozostaje takie samo, niezależnie od tego, czy jest to 0, czy 1.

S to 0, a R to 1: Zatrzmieć resetuje, zmuszając wyjście Q do 0.

S to 1, a R to 0: Zestaw zatrzaski, dzięki czemu wyjście Q jest równe 1.

Zarówno S, jak i R to 1: Ten warunek jest nieprawidłowy lub niezdefiniowany, często określany jako stan „zabroniony” w zatrzasku SR.W tym przypadku q i q 'zarówno równe 0, co prowadzi do niejednoznacznego wyjścia.

Gdy s i r mają 0, zatrzask nic nie robi i po prostu utrzymuje swoją bieżącą wartość.Jest to przydatne do utrzymania stanu bez zmian.

Kiedy S wynosi 0, a R to 1, zatrzask jest wyraźnie powiedziany do zresetowania, upewniając się, że Q ma 0, niezależnie od jego poprzedniego stanu.Jest to prosty sposób na wyczyszczenie zatrzasku.

Gdy S wynosi 1, a R wynosi 0, zatrzask jest ustawiony, zapewniając, że Q staje się 1. W ten sposób przechowywasz „1” w zatrzasku.

Gdy s i r są 1, stan nie jest dozwolony, ponieważ powoduje, że oba wyjścia wynoszą 0, co jest sprzeczne i niewiarygodne.Projektanci muszą unikać tego warunku, aby zapewnić stabilne działanie.

Zalety i wady zatrzasków

Zatrzymania są szeroko stosowane w projektowaniu obwodów cyfrowych ze względu na ich prostotę i niski koszt.Te cechy umożliwiają zatrzaski działanie przy dużych prędkościach o niskim zużyciu energii, dzięki czemu są idealne do szybkich systemów cyfrowych.Na przykład w plikach rejestrujących procesor zatrzaski mogą szybko przechowywać i pobierać dane, znacznie zwiększając prędkość i wydajność przetwarzania.

Zalety zatrzasków

Prostota i opłacalność: zatrzaski są prostymi komponentami, które są niedrogie w wdrażaniu w obwodach cyfrowych.

Duchowa i niska moc: ich konstrukcja pozwala na szybkie działanie przy minimalnym zużyciu energii, co ma kluczowe znaczenie w szybkich systemach cyfrowych.

Wydajność obsługi danych: W aplikacjach takich jak pliki rejestru procesora zatrzaski zapewniają szybkie przechowywanie danych i wyszukiwanie, zwiększając ogólną wydajność systemu.

Wady zatrzasków

Pomimo ich zalet zatrzaski mają znaczące ograniczenia w niektórych projektach i zastosowaniach.

Nieprzewidywalne zachowanie w projektach asynchronicznych: bez kontroli sygnału zegara zatrzaski mogą zachowywać się nieprzewidywalnie.W zatrzaskach SR, jeśli oba ustawienia (-y) i reset (R) są wysokie jednocześnie, wyjście staje się niezdefiniowane, co prowadzi do niestabilności.Jest to problematyczne w zastosowaniach kontroli w czasie rzeczywistym lub krytycznym bezpieczeństwem, w których niezawodne wyjście jest kluczowe.

Złożony projekt czasu: Projektowanie za pomocą zatrzasków wymaga starannych rozważań dotyczących czasu.Inżynierowie muszą uwzględniać opóźnienia propagacji sygnału i warunki wyścigu, aby uniknąć błędów czasowych.Niewłaściwy projekt może powodować zmiany danych, zanim sygnał zegara się ustabilizuje, powodując uszkodzenie danych lub nieprawidłowe przechwytywanie danych.Wymaga to głębokiego zrozumienia analizy czasu i zachowania obwodu.

Aby sprostać tym wyzwaniom, można zastosować konkretne techniki projektowe i strategie:

Mechanizmy synchronizacji: Dodanie mechanizmów synchronizacji może pomóc w zarządzaniu wejściami asynchronicznymi i złagodzić nieprzewidywalne zachowanie.

Niestandardowe zarządzanie zegarkiem: wdrażanie dostosowanych strategii zarządzania zegara może zapewnić poprawnie i we właściwym momencie.

Korzystanie z narzędzi EDA: Modern Electronic Design Automation (EDA) Narzędzia oferują zaawansowane możliwości analizy i optymalizacji.Narzędzia te pomagają przewidywać i rozwiązać problemy czasowe i synchronizacyjne podczas fazy projektowej, poprawia niezawodność i wydajność systemów cyfrowych za pomocą zatrzasków.Pomagają projektantom we wczesnym identyfikacji potencjalnych problemów, zapewniając niezawodnie działanie produktu końcowego w różnych warunkach.

Praktyczne zastosowania zatrzasków SR

Zatrzaski SR, znane ze swojej zdolności do szybkiego i niezawodnego utrzymywania stanu, są szeroko stosowane w różnych systemach elektronicznych.Excent one w scenariuszach wymagających tymczasowego przechowywania danych lub zatrzymywania stanu.

Tymczasowe przechowywanie danych

Zatrzęcie SR są często używane w pamięci pamięci podręcznej do tymczasowego przechowywania danych.Umożliwia to systemowi szybki dostęp do często używanych danych, znacznie zwiększając możliwości przetwarzania danych i wydajność na dużą skalę procesorów.

Pliki rejestru przechowywania

W procesorach zatrzaski SR umożliwiają szybkie przechowywanie i pobieranie danych w plikach rejestru, zwiększając prędkość przetwarzania i ogólną wydajność systemu.

Utrzymanie sygnałów kontrolnych

W systemach sterowania cyfrowym zatrzaski SR są przydatne w utrzymywaniu stanu niektórych sygnałów kontrolnych, dopóki warunki zewnętrzne lub logika systemu nie wykryje zmiany.Pomagają również w utrzymaniu stanów w systemie, zapewniając spójną wydajność w operacjach wymagających precyzji i niezawodności.

Wyzwalacz i obwody kontratakowe

Flip-klapy oparte na zatrzasku SR są powszechnie stosowane w obwodach wymagających zsynchronizowanej operacji, takich jak zegary cyfrowe i timery.Kontrolują impulsy liczby, zapewniając dokładne wykonywanie czasu i niezawodne wydajność.Obwody te opierają się na zatrzaskach SR w celu utrzymania dokładnych zliczeń, co ułatwia czas i sekwencjonowanie w systemach cyfrowych.

Interakcje mechaniczne

Zatrzęcie SR skutecznie eliminują odbicie mechaniczne w przełącznikach.Odbicie mechaniczne występuje, gdy przełącznik generuje szybkie, powtarzalne zmiany sygnału z powodu słabego kontaktu.Zatrzęcie SR stabilizują sygnał wyjściowy, zapobiegając błędom spowodowanym przez hałaśliwe sygnały.

SR Flip-Flop

Flip-flop SR, często nazywany flip-flip-flip-flip-flip-flip-flip-flip-flip-flip, składa się z dwóch połączonych zatrzasków SR.Ta struktura z podwójnym zatrzaskiem pozwala mu reagować na określone krawędzie sygnału zegara (wznoszącego się lub spadające), aby zmienić jego stan.Osiąga się to poprzez specjalną kontrolę logiczną między zatrzaskami.Wyjście pierwszego zatrzasku staje się częścią wejścia dla drugiego zatrzasku, a wyjście drugiego zatrzasku wpływa z kolei pierwszego zatrzasku, tworząc blokującą pętlę sprzężenia zwrotnego.

Rysunek 7: Flip-flop SR

Flip-Flop SR zmienia się dokładnie na rosnącej krawędzi lub spadającej krawędzi sygnału zegara.Zamknięte informacje zwrotne między dwoma zatrzaskami SR zapewnia, że flip-flop zmienia tylko stan w odpowiedzi na krawędź zegara, zapewniając stabilne i niezawodne wyjście.

W mikroprocesorach i cyfrowych procesorach sygnałów sr flip-klapy są używane do pobierania próbek i przechowywania danych.Przechwytują i stabilizują dane na określonych krawędziach zegara, zapewniając wiarygodne późniejsze przetwarzanie i analiza danych.

Mechanizm wyzwalania krawędzi pomaga uniknąć warunków rasy, w których różne części obwodu mogą jednocześnie zmieniać stan bez synchronizacji, potencjalnie powodując niestabilne lub nieprawidłowe wyjście.Flip-klapy SR są kluczowe we wdrażaniu określonej logiki protokołu komunikacji, takich jak synchronizacja ramek i wykrywanie błędów.Ich stabilność i szybki czas reakcji pomagają utrzymać jakość transmisji danych i niezawodność systemu.

Zakazane stany w zatrzaskach SR i klapkach SR

Projektując zatrzaski SR i klapki SR za pomocą NAND i NOT GATES, wszyscy musimy zwrócić uwagę na zarządzanie i unikanie zahamowanych stanów.Stan zakazujący występuje, gdy zarówno dane wejściowe z zestawu (ów), jak i reset (R) są jednocześnie wysokie (dla bram NAND) lub niskie (dla bramek).Ta kombinacja prowadzi do nieokreślonego stanu wyjściowego, ponieważ wyjście zależy od poprzedniego stanu obwodu, co czyni go nieprzewidywalnym.

Zakazane stany w zatrzaskach Nand Gate SR

Gdy zarówno S, jak i R są niskie, oba wyjścia są wysokie, co narusza uzupełniającą się charakterystykę wyjściową zatrzasku.Powoduje to stan nieokreślony.

Zakazane stany w zatrzaskach ani bramki

Gdy zarówno S, jak i R są wysokie, oba wyjścia są niskie, tworząc również stan nieokreślony.Może to prowadzić do nieprzewidywalnego zachowania w obwodzie.

Praktyczne podejścia, aby uniknąć zakazanych stanów

Dodanie logiki sterowania

Użyj dodatkowych bram logicznych do monitorowania stanów S i R. Jeśli oba dane wejściowe trenują w kierunku stanu zabronionego, automatycznie dostosuj jedno wejście, aby zapobiec stanowi nieokreślonemu.Zapewnia to, że wyjścia pozostają stabilne i przewidywalne.Zaimplementuj bramę logiczną, która interweniuje, gdy S i R są wysokie (lub niskie), dostosowując jedno wejście w celu utrzymania prawidłowego stanu.

Symulacja oprogramowania i testowanie sprzętu

Przeprowadź dokładne symulacje oprogramowania w celu zidentyfikowania potencjalnych zakazanych stanów w różnych warunkach pracy.Pozwala to projektantom wykryć i korygować błędy logiczne przed fizyczną implementacją.Wykonaj obszerne testy sprzętowe, aby poprawnie obsługiwać wszystkie kombinacje wejściowe.Ten krok pomaga zapewnić, że zatrzask lub flip-flop działał niezawodnie w scenariuszach w świecie rzeczywistym.

Wniosek

Wszechstronność i niezawodność zatrzasków SR podkreślają ich znaczenie w projektowaniu obwodów cyfrowych.Badając niuansowe zachowanie zatrzasków SR poprzez ich symbol reprezentacje, tabele prawdy i praktyczne zastosowania, zyskujemy kompleksowe zrozumienie ich działania i znaczenia.Pomimo potencjalnych pułapek nieokreślonych stanów w projektach asynchronicznych strategiczne wdrożenie logiki kontroli i obszerna symulacja może złagodzić te ryzyko.Narzędzia Advanced Electronic Design Automation (EDA) dodatkowo zwiększają niezawodność i wydajność obwodów zawierających zatrzaski SR poprzez przewidywanie i rozwiązywanie problemów czasowych i synchronizacji.Niezależnie od tego, czy jest używany w tymczasowym przechowywaniu danych, konserwacji sygnału sterowania lub wykryciu błędów, zatrzaski SR okazują się fundamentalne w tworzeniu solidnych i wydajnych systemów cyfrowych.Ich rola w szybkich operacjach pamięci i synchronicznym przetwarzaniu danych w złożonych aplikacjach jest przykładem ich trwałego znaczenia.Wraz z postępem technologii zasady regulujące zatrzaski SR nadal informują i inspirują innowacje w zakresie elektroniki cyfrowej, zapewniając, że te elementarne komponenty pozostają integralną częścią rozwoju wyrafinowanych i niezawodnych urządzeń elektronicznych.

Często zadawane pytania [FAQ]

1. Co to jest zatrzask SR?

Zatrzask SR lub zatrzask set-reset to podstawowy element magazynowy binarny używany w obwodach cyfrowych.Jest to obwód asynchroniczny, co oznacza, że działa bez sygnału zegara, opierając się na bezpośredniej kontroli jego danych wejściowych w celu zmiany stanów.

2. Jaka jest funkcja SR w logice?

W logice wprowadza SR (SET-RESET) kontrolują stan zatrzasku.

3. Jakiego rodzaju bramki logicznej używa SR?

Zatrzask SR zwykle używa ani bram ani bram NAND.W zatrzasku SR opartym na bramie wyjście każdej bramki NOR jest podawane z powrotem do wejścia drugiej, tworząc stabilną pętlę sprzężenia zwrotnego.W zatrzasku SR opartym na bramie NAND stosuje się podobną konfigurację sprzężenia zwrotnego, ale poziomy logiki są odwrócone w porównaniu z zatrzaskiem opartym na bramie ONO.Obie konfiguracje osiągają tę samą podstawową funkcjonalność utrzymywania stanu binarnego na podstawie zestawu i resetowania wejść.

4. Jak działa zatrzask?

Zatrzmieć działa przy użyciu informacji zwrotnej w celu utrzymania stanu wyjściowego w oparciu o dostarczone dane wejściowe.W zatrzasku SR zestaw i reset (r) wprowadzają stan wyjścia (q).Gdy wejście ustawione jest aktywowane (wysokie), wyjście jest ustawione na wysokie (1).Gdy wejście resetowania jest aktywowane (wysokie), wyjście jest resetowane do niskiego (0).Pętla sprzężenia zwrotnego w projekcie zatrzasku zapewnia, że po ustaleniu stanu wyjściowego pozostaje stabilna, dopóki nowy sygnał wejściowy go nie zmieni.

5. Jaka jest wada z zatrzaskiem SR?

Podstawową wadą zatrzaski SR jest nieokreślony stan, który występuje, gdy oba ustawienia (r) wejścia (r) są wysokie.Ten warunek prowadzi do nieokreślonego stanu wyjściowego, który może powodować niestabilność i nieprzewidywalne zachowanie w obwodach cyfrowych.Należy uniknąć tego stanu „zabronionego”, aby zapewnić niezawodne działanie.

SR Zatrzęcanie się, zatrzask set-reset, obwód asynchroniczny, element magazynowy binarny, obwody cyfrowe, ani bramy, bramy nand, pętla sprzężenia zwrotnego, wysoki stan, niski stan, stan niezdefiniowany, sygnał zegara, kontrola bezpośrednia, tymczasowe przechowywanie danych, przechowywanie wyników pośrednich,Wykrywanie błędów, zastosowania lotnicze, urządzenia medyczne, projektowanie obwodu, zatrzask SR, sygnały wejściowe, symbol i struktura, pamięć szybkich, bufory danych, kontrola czasu, precyzyjna kontrola, retencja stanu, mikroprocesory, cyfrowe procesory sygnałów, próbkowanie danych, dane danych,Przechowywanie, wyzwalane przez krawędź, Flip-Flop SR, blokujące sprzężenie zwrotne, warunki rasy, logika protokołu komunikacji, synchronizacja ramek, wykrywanie błędów, usterki sygnałowe, automatyzacja projektowania elektronicznego, narzędzia EDA, mechanizmy synchronizacji, niestandardowe zarządzanie zegarWarunki wyścigowe, złożone transfery danych, systemy zarządzania energią, odbicie mechaniczne, praktyczne aplikacje, cyfrowe systemy sterowania, bramy logiczne, symulacje oprogramowania, testowanie sprzętu, stany zabronione, niezawodność zatrzasku.