Zrozumienie zatrzasków w systemach cyfrowych

W cyfrowej elektronice potrzebna jest poprawa części obwodów, aby uzyskać lepszą stabilność systemu i funkcję.Jednym dużym krokiem jest przejście z zatrzasków SR do zatrzasków D.Zatrzęcie dają wkłady prostsze i ograniczają niezdefiniowane stany, co czyni je lepszymi w projektowaniu i niezawodnym w systemach pamięci cyfrowej.W tym artykule dotyczy projektu D Lotch, How Its It i jego zastosowań, podkreślając jego znaczenie w nowoczesnych obwodach.Omówimy jego podstawową strukturę, sposób, w jaki działa i jak pasuje do złożonych systemów z multiplekserami.Badając te aspekty, rozumiemy, w jaki sposób D Latch poprawia integralność danych i przewidywalność w systemach cyfrowych, zwiększając wydajność i niezawodność komponentów elektronicznych.Katalog

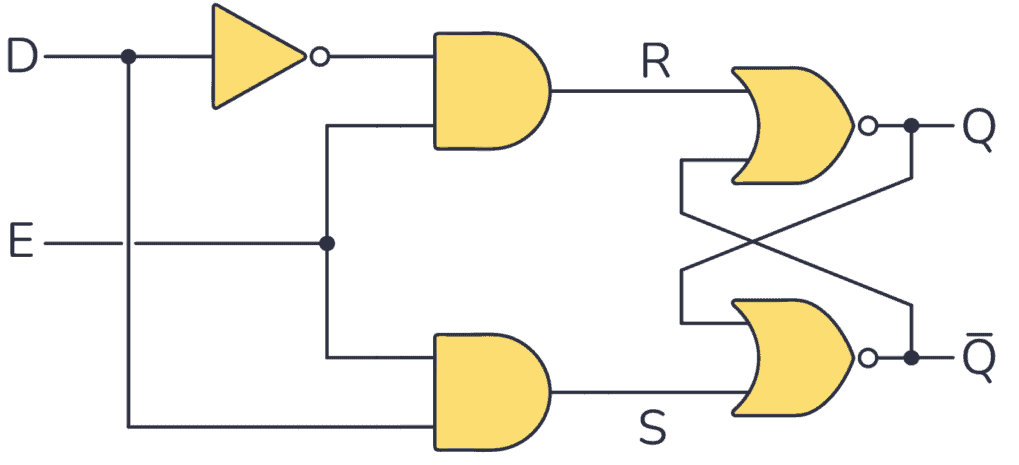

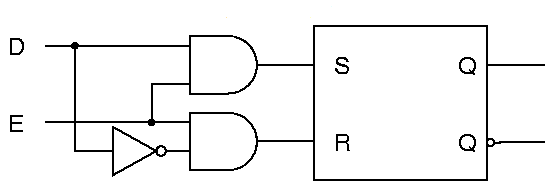

Rysunek 1: Zatrzęcanie D

Obwody zatrzasne D

Opracowanie elektronicznych obwodów zatrzasnych odnotowano wiele ważnych zmian, co prowadzi do stworzenia zatrzasku D, lepszej wersji zamkniętego zatrzasku S-R.Początkowo bramkowane zatrzaski S-R użyły zestawu (reset (R) (R), zarządzane przez sygnał włączalny do kontroli, gdy zatrzask będzie działał.Jednak te wczesne projekty miały problemy z nieokreślonymi stanami, co może spowodować awarię systemu.Usuwając wejście resetowania i używając przeciwieństwa danych wejściowych jako jedynej metody sterowania, proces wejściowy stał się znacznie prostszy, dzięki czemu system jest bardziej przewidywalny i łatwiejszy w użyciu.Ta zmiana zapewniła, że wyjścia, Q i not-Q, były zawsze przeciwieństwami, dzięki czemu operacja jest bardziej stabilna i niezawodna.

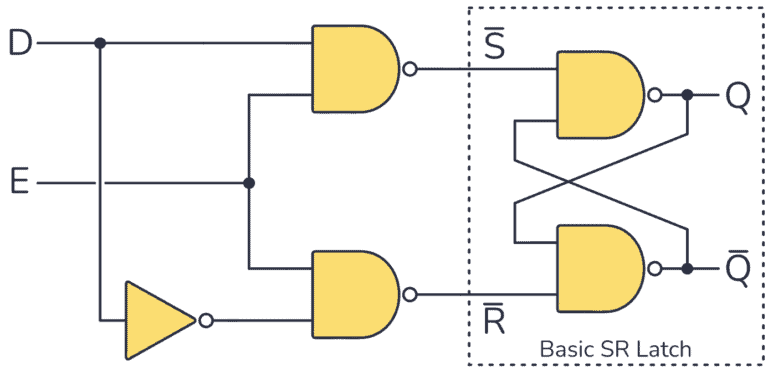

Rysunek 2: D symbol zatrzasku

Struktura zatrzasku D

Główną cechą zatrzasku D jest jego system jednomyślny, który zastępuje konstrukcję dwóch wejściowych starszego zatrzasku S-R.To pojedyncze wejście, zwane wejściem danych (D), upraszcza działanie zatrzasku.

W zatrzasku D wyjście jest kontrolowane przez dwa sygnały: wejście danych (D) i sygnał włączalny (E).Gdy sygnał Włącz jest aktywny, dane wejściowe danych (D) określa stan wyjścia (Q).Jeśli wejście danych wynosi 1, wyjście (q) również wynosi 1. Jeśli wejście danych wynosi 0, wyjście (q) wyniesie 0. Drugie wyjście, nie-Q, jest zawsze przeciwieństwem Q.że jeśli Q wynosi 1, not-Q będzie 0 i odwrotnie.

Ten związek między Q i NOT-Q zapewnia, że wyjścia są zawsze przewidywalne i stabilne.Struktura zatrzecia D eliminuje problemy znalezione w starszym zatrzasku S-R, gdzie posiadanie dwóch danych wejściowych może czasami prowadzić do nieokreślonych stanów.Te niezdefiniowane stany mogą spowodować awarię obwodu.

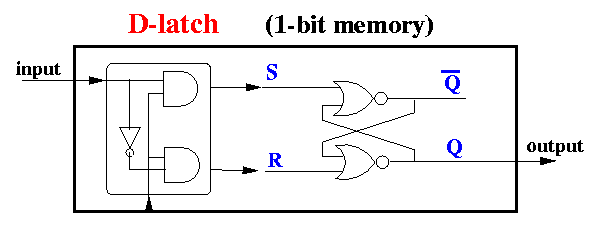

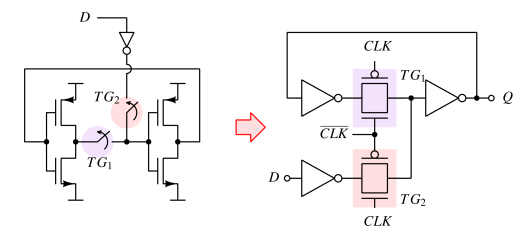

Rysunek 3: D obwód zatrzasny

Standaryzowane zatrzaski D w elektronice

Zatrzęcanie D nie jest po prostu teoretycznym pomysłem.To prawdziwa, integralna część znaleziona w wielu elektronikach.Można go znaleźć jako komponent obwodu wstępnie zapakowanego, co oznacza, że jest gotowy i łatwy w użyciu w każdym projektach.W schematach elektronicznych zatrzask D pokazuje standardowy symbol, co ułatwia rozpoznanie i zrozumienie.Ten znormalizowany symbol jest ważny, ponieważ pokazuje, jak szeroko stosowany zatrzask D w branży elektronicznej.

Zatrzmieć D działa jako podstawowa jednostka pamięci w dowolnych rodzajach systemów obliczeniowych.Pomaga przechowywać i śledzić dane binarne, najlepiej do prawidłowego funkcjonowania tych systemów.Ponieważ zatrzask D jest znormalizowany, zapewnia, że jego funkcjonalność jest spójna w zastosowaniach elektronicznych.

Rysunek 4: D Zatrzęcanie się w pamięci

Rola darze D w systemach pamięci cyfrowej

Działa, umożliwiając wprowadzanie danych, gdy sygnał włączania jest wysoki.Gdy ten sygnał jest wysoki, wszelkie dane są przechwytywane i utrzymywane przez zatrzask D.Gdy tylko sygnał Włącz spadnie do niskiego poziomu, zatrzask D przestaje akceptować nowe dane i utrzymuje ostatni otrzymany kawałek danych.I utrzymuje stabilne i niezmienione dane, nawet jeśli występują zmiany w danych przychodzących po wyłączeniu sygnału włączonego.Ta charakterystyka zatrzasku D jest niezwykle ważna dla przechowywania pamięci.Oznacza to, że po przechowywaniu danych pozostaje bezpieczna i niezmieniona, co jest dobre dla integralności danych, szczególnie w systemach, w których dane muszą być wiarygodne i stałe w czasie.Zdolność D Latch do niezawodnego utrzymywania pojedynczych danych w różnych warunkach sprawia, że jest to główny odtwarzacz w systemach pamięci pamięci.Jest to szczególnie skuteczne w środowiskach, w których dane powinny być dokładnie przechowywane.Zatrzęcanie D jest wysoce przystosowalne, co czyni go cennym w aplikacjach cyfrowych.W programowalnych sterownikach logicznych może zastąpić tradycyjne zatrzaski S-R na schematach logicznych drabin, pokazując jego elastyczność w środowiskach elektronicznych i obliczeniowych.Ta wszechstronność zapewnia, że zatrzask D pozostaje istotny w szybko rozwijającej się technologii.

Rysunek 5: 4-bitowa pamięć skonstruowana za pomocą czterech zatrzasków D

Projektowanie i analiza obwodu zatrzasku D

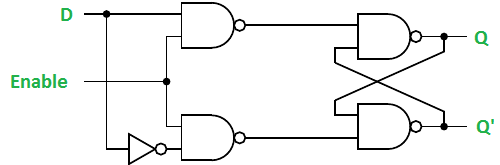

Rysunek 6: D obwód zatrzasny i bramy logiczne

Zatrzmieć oznacza pozytywny postęp w projektowaniu obwodów cyfrowych poprzez rozwiązanie ograniczeń zatrzasku SR.Przezwycięży problem stanów nieokreślonych spowodowanych, gdy oba ustawione (-y) i reset (r) wejścia są wysokie w zatrzasku SR.Ta poprawa osiąga się poprzez uproszczenie schematu wejściowego do pojedynczego wejścia danych, znanego jako D, i wprowadzenie falownika w celu zapewnienia, że dane wejściowe są zawsze komplementarne.

Ten projekt oferuje pewne zalety.Przede wszystkim gwarantuje przewidywalne przejścia stanu na podstawie wartości wejścia D.Gdy D jest niski, następny stan zatrzasny jest ustawiony na zero;Gdy D jest wysoki, następny stan jest ustawiony na jeden.Ta przewidywalność bezpośrednio odzwierciedla tabelę prawdy SR zatrzasku, ale z zwiększoną niezawodnością.D Latch utrzymuje integralność danych, o ile jest spełniony warunek włączania, co czyni go dobrym w obwodach cyfrowych, szczególnie w aplikacjach wymagających niezawodnego przechowywania danych, takich jak urządzenia pamięci i elementy rejestru.

Rysunek 7: falownik darem d-na drugim

Konstruowanie zatrzaski D za pomocą podstawowych elementów cyfrowych, takich jak NAND Gates and Falterters, zapewnia namacalne zrozumienie jego działania i korzyści.To praktyczne podejście jest szczególnie przydatne w warunkach edukacyjnych, umożliwiając uczniom i entuzjastom obserwowanie i analizowanie zachowania zatrzasku w różnych warunkach.Poprzez praktyczne eksperymenty uczniowie zyskują głębszy wgląd w cyfrową pamięć pamięci i kontrolę sygnału.Obserwowanie, w jaki sposób zatrzask D reaguje na wiele danych wejściowych i utrzymuje swój stan, wzmacnia znaczenie projektowania obwodów w osiąganiu wiarygodnej funkcjonalności cyfrowej.Eksperymentacja to podkreśla potrzebę uzupełniających się nakładów, aby uniknąć stanów nieokreślonych, umacniając zasady projektowania zatrzasku cyfrowego ucznia.

Obwód zatrzasny D poprawia zatrzask SR poprzez dodanie bram logicznych, aby zapobiec nieprawidłowym stanom i poprawić funkcjonalność.Falownik na wejściu D, w połączeniu z bramami NAND, wprowadza wejście (e), które kontroluje po przechwytywanie danych.Ta konfiguracja zapewnia, że zatrzask przechwytujący dane z wejścia D do wyjścia Q, gdy sygnał włączania jest aktywny, zapewniając precyzyjną kontrolę dla buforowania danych i aplikacji czasowych.Udoskonalenie adaptacji obwodu jest dalej wykazane przez potencjalne konfiguracje przy użyciu wielu typów bram, takich jak i nor i bramy, pokazując jego wszechstronność w cyfrowym scenariuszach logicznych.

Rysunek 8: Modyfikowanie zatrzaski na bazie falownika na podstawie użytecznego D lech

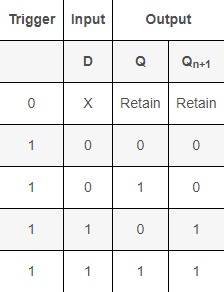

D Tabela prawdy zatrzasku

Zrozumienie wytycznych operacyjnych dokuczania D jest wymagane do jego zastosowania w obwodach cyfrowych.Tabela prawdy D zatrzasków zawiera wyraźny przegląd, w jaki sposób zatrzask reaguje na kombinacje sygnałów wejściowych i zegarowych.Ta tabela prawdy jest odpowiednim narzędziem dla projektantów, umożliwiając im przewidywanie zachowania zatrzasku w różnych warunkach i upewnienie się, że funkcje obwodu prawidłowe w zamierzonych aplikacjach.

Rysunek 9: D Tabela prawdy zatrzasku

Analiza obwodu zatrzasku D

Szczegółowa analiza obwodu zatrzasku D pokazuje strategiczny układ bram NAND, które utrzymują integralność sygnału i zapobiega konfliktom państwowym.Ścieżka od wejścia do wyjścia jest starannie odwzorowana, co pokazuje, w jaki sposób każdy komponent zapewnia poprawnie funkcje zatrzask w różnych warunkach.Ten podział jest odpowiedni do zrozumienia, w jaki sposób zatrzask D osiąga spójną niezawodność, podkreślając precyzję wymaganą w projektowaniu obwodów cyfrowych.

Zatrzęcie D jest wymaganym komponentem pamięci w obwodach cyfrowych, zdolnych do zachowania jego bieżącego stanu lub zaktualizowania go w oparciu o wejście włączające.To zachowanie jest opisane w tabeli prawdy D zatrzasku.Gdy wejście włączające jest niskie, zatrzask ignoruje zmiany przy wejściu D, utrzymując jego obecny stan.Gdy wejście Włącz jest wysokie, wyjście Q pasuje do wejścia D.W systemach pamięci cyfrowej i obwodach logicznych pojemność D zatrzymania lub selektywnej aktualizacji zapewnia stabilność danych i przewidywalne wyniki.Dynamika czasu zatrzasku D jest najlepiej zrozumieć poprzez schemat taktowania, który pokazuje, w jaki sposób wejście i wyjście oddziałują z sygnałem włączonym.Gdy włączenie jest aktywne, wyjście Q odzwierciedla wejście D. Gdy włączenie jest nieaktywne, zatrzask zachowuje swój ostatni stan.Pomocne może być zrozumienie zachowania darem d w odniesieniu do zmian sygnału włączonego, szczególnie poprzez zastosowanie tej reprezentacji graficznej.Te spostrzeżenia są cenne do projektowania, rozwiązywania problemów i optymalizacji obwodów zawierających zatrzask D.Badanie konstrukcji darze D poprzez falowniki z tyłu ujawnia alternatywne podejścia, które spełniają określone wymagania i ograniczenia projektowania elektronicznego.Ta metoda podkreśla zdolność adaptacyjną D Latch i innowacyjny potencjał w zakresie roztworów pamięci cyfrowej.

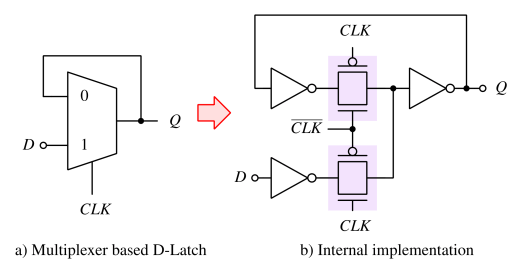

Design d-zatrzask oparty na multiplekserze

Rysunek 10: Zatrzasek d oparty na multiplekserze

Dalsze usprawnienie i dostosowywanie zatrzasku D można osiągnąć poprzez włączenie multipleksera (MUX).Multiplekser wybiera między różnymi wejściami danych na podstawie sygnału sterującego, umożliwiając daczowi D obsługę wielu źródeł danych w tej samej konfiguracji obwodu.Ta zdolność jest szczególnie przydatna w złożonych systemach, w których wiele danych wejściowych powinno być przetwarzane i przechowywane warunkowo.Integracja multipleksera z zatrzaskiem D zwiększa funkcjonalność poprzez uwzględnienie wielu źródeł wejściowych przy jednoczesnym zachowaniu prostoty projektu zatrzasku.Jest to korzystne w aplikacjach wymagających szybkiego przełączania między różnymi wejściami danych w kontrolowanych warunkach czasowych, takich jak systemy komunikacyjne lub złożone jednostki obliczeniowe.Korzystanie z multipleksera do utworzenia zatrzaski D podkreśla elastyczność projektowania zatrzasku, pokazując, w jaki sposób można ponownie skonfigurować standardowe komponenty cyfrowe do wykonywania podobnych funkcji na wiele sposobów.Ta metoda zwiększa zrozumienie cyfrowych zasad projektowania logiki i ich praktycznych zastosowań, zwiększając wszechstronność w projektowaniu obwodów.

Standard zamkniętych zatrzasków D

Rysunek 11: Obrażowy obwód zatrzasny D.

Diagram logiczny zamkniętego darze d

Schemat logiczny zamkniętego darze D jest kluczowym narzędziem do budowania i analizy tych obwodów cyfrowych.Pokazuje, jak działa obwód szczegółowo, co jest dobre do projektowania lub utrzymywania cyfrowych systemów elektronicznych.Pokazując każde połączenie i komponent, schemat pomaga zrozumieć, jak działa zatrzask D.

Rysunek 12: Schemat logiczny zamkniętego darze d

Ten schemat pokazuje również ulepszenia w stosunku do podstawowego zatrzasku D.Jedną z głównych ulepszeń jest dodanie dodatkowych mechanizmów kontroli w celu lepszego przechowywania i pobierania danych.Zmiany te sprawiają, że zamknięte daźnie D jest bardziej niezawodne i wydajne, zwiększając jego wydajność w cyfrowej elektronice.

Ulepszenia obejmują funkcje takie jak włączenie i wyłączenie zatrzaski na podstawie sygnałów kontrolnych, które zapobiegają niepożądanym zmianom danych podczas trudnych operacji.Utrzymuje to dokładność danych podczas działania obwodu, który jest częścią złożonych systemów cyfrowych, w których ważna jest precyzja.Schemat logiczny służy jako przewodnik do budowania lub naprawy zamkniętego zatrzasku D i pomaga lepiej zrozumieć obwody cyfrowe.

Rola zamkniętego darze D w obwodach cyfrowych

Dodanie bramkowania do projektu D Latch poprawia kontrolę w obwodach cyfrowych, dzięki czemu przechowywanie danych jest bardziej przewidywalne i stabilne.Gramat D zatrzask pozwala na kontrolę danych, dostosowując pamięć z określonymi fazami operacyjnymi w systemach cyfrowych.To precyzyjne prawo do aplikacji wymagających dokładnego czasu i ścisłego zarządzania państwem w zaawansowanych obwodach cyfrowych.Jako podstawowy element pamięci, zatrzask D jest potrzebny do zarządzania zmianami stanu i danych w obwodach cyfrowych.Utrzymanie integralności danych i niezawodności wymaga precyzyjnego czasu i dokładnego wprowadzania danych.Zatrzmieć D przechwytuje i przechowuje dane na podstawie sygnałów sterowania, zapewniając, że aktualizacje zdarzają się tylko we właściwych momentach, co zapobiega błędom i uszkodzeniu danych.

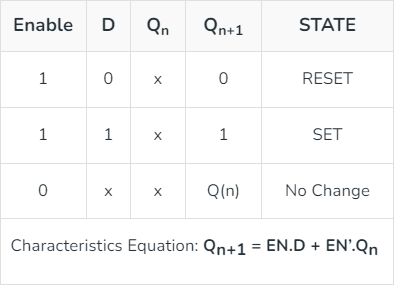

Tabela prawdy zamkniętej darze

Tabela prawdy dla zamkniętego D zatrzaski przedstawia określone wyniki w oparciu o warunki wejściowe.Służy jako ostateczny przewodnik do przewidywania zachowania zatrzasku w scenariuszach, zwiększając projekt i funkcjonalność obwodów cyfrowych, które wykorzystują ten komponent.

Rycina 13: Tabela prawdy zamkniętej darze d

Wniosek

Znajomość darze D pokazuje swoją rolę w zwiększaniu wydajności nowoczesnych systemów cyfrowych.W przeciwieństwie do starszych zatrzasków SR, zatrzask D zapewnia przewidywalność i stabilność, szczególnie w przypadku dzisiejszej technologii.Jego prosty system wejściowy zapobiega niepewnym stanom i utrzymuje dane nienaruszone w różnych warunkach.Zastosowanie multiplekserów i bramkowanych wersji pokazuje elastyczność i ciągły rozwój D Latch w celu zaspokojenia zaawansowanych potrzeb technologicznych.Jego standardowe zastosowanie na dowolnych platformach potwierdza jego znaczenie w projektowaniu obwodów cyfrowych.W tym artykule pokazano techniczne korzyści płynących z D uderzenia D i jego duży wpływ na rozwój systemu pamięci cyfrowej, co czyni go najlepszym narzędziem dla inżynierów i projektantów w zakresie elektroniki cyfrowej.

Często zadawane pytania [FAQ]

1. Co to jest zatrzask D?

Zatrzmieć D (zatrzask danych lub przezroczysty zatrzask) jest prostym typem obwodu Flip-Flop, używanego przede wszystkim do przechowywania danych binarnych.Składa się z wejścia danych, wyjścia i wejścia sygnału sterującego, powszechnie określanego jako wejście włączania lub zegara.Podstawową częścią zatrzaski D jest przechwytywanie i utrzymanie binarnej wartości wejściowej, dzięki czemu jest dostępna na wyjściu, o ile na to pozwala sygnał sterujący.

2. Jaka jest funkcja zamkniętego zatrzasku D?

Gramat d zatrzaski działa jako urządzenie do przechowywania danych, które umożliwia przechowywanie i pobieranie danych w oparciu o stan jego sygnału sterowania.Gdy wejście Enable (lub zegar) jest aktywne, zatrzask „słucha” wejścia danych i przekazuje je do wyjścia.Gdy wejście włączające jest nieaktywne, wyjście zachowuje ostatnią wartość danych, która została wprowadzona, podczas gdy sygnał włączania był aktywny.

3. Na której bramie jest zatrzask D?

Zatrzęcie D jest zazwyczaj oparte na NAND lub bramach.Bramy te są skonfigurowane w taki sposób, że tworzą pętlę sprzężenia zwrotnego, umożliwiając urządzeniu utrzymanie stanu wyjściowego (przechowywania danych) nawet po zmianach warunków wejściowych.

4. Jak zrobić zatrzask D?

Aby skonstruować zatrzask D, zaczynasz od zorganizowania NAND lub bram w obwód sprzężenia zwrotnego.Podstawowa konfiguracja polega na użyciu dwóch bram do utworzenia pętli, która utrzymuje wyjście do momentu zmiany sygnału sterowania.Podłącz dane wejściowe danych do jednej z bramek, którego wyjście przekazuje się do drugiej bramy, która z kolei kontroluje operację pierwszej bramki w oparciu o warunki włączania sygnału.

5. Jaka jest funkcja zatrzasku D?

Jak wspomniano, funkcją zatrzasku D jest przechowywanie pojedynczego bitu danych i zapewnienie stabilnego wyjścia, o ile sygnał sterujący pozostaje niezmieniony.Służy jako podstawowa jednostka pamięci w systemach elektronicznych, rejestrowanie i utrzymywanie danych dynamicznie zgodnie z wymogami systemu.

6. Dlaczego Gated D zatrzaska nazywa się przezroczystą zatrzask?

Gatkowany zatrzask D jest nazywany przezroczystym zatrzaskiem, ponieważ gdy sygnał włączający jest aktywny, zmiany na wejściu danych są bezpośrednio odzwierciedlone przy wyjściu, a następnie sprawiają, że zatrzask „przezroczysty” do przejścia danych.Ta przejrzystość ma przetwarzanie danych w czasie rzeczywistym, w którym potrzebne są natychmiastowe aktualizacje wyjścia.

7. W jaki sposób D Latch przechowuje dane?

D Latch przechowuje dane za pomocą mechanizmu pętli zwrotnej.Gdy sygnał Włącz jest aktywny, wejście danych jest zasilane przez bramy w celu ustawienia stanu wyjściowego.Gdy tylko włączenie staje się nieaktywne, wyjście bramek jest zapętlone z powrotem do jego wejść, utrzymując ostatni stan na czas nieokreślony, dopóki włączenie zostanie ponownie aktywowane za pomocą nowych danych.To zapętlanie wyjścia do wejścia jest tym, co umożliwia zatrzymanie danych bez zewnętrznego odświeżania.